Hello,

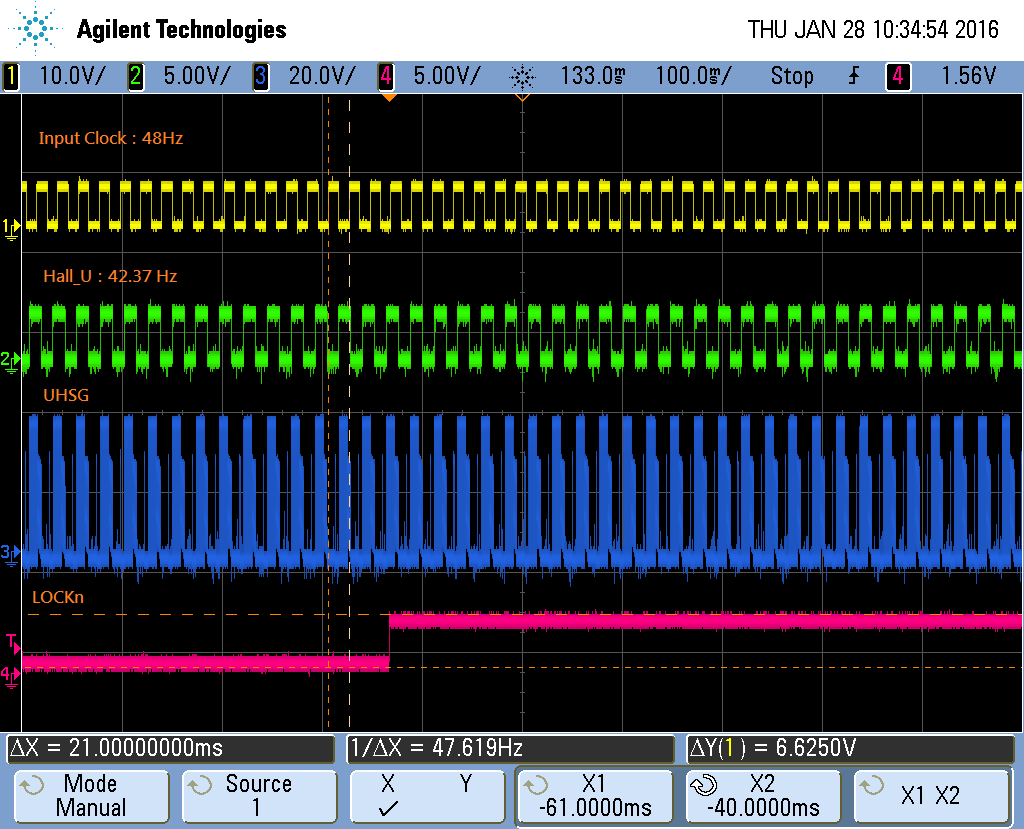

Customer use register mode and it can spin the motor and will let speed LOCKn to low. But when use clock mode of drv8308, it can not let LOCKn to low but fCLKIN and FGOUT are most the same frequency. What is the issue root cause?

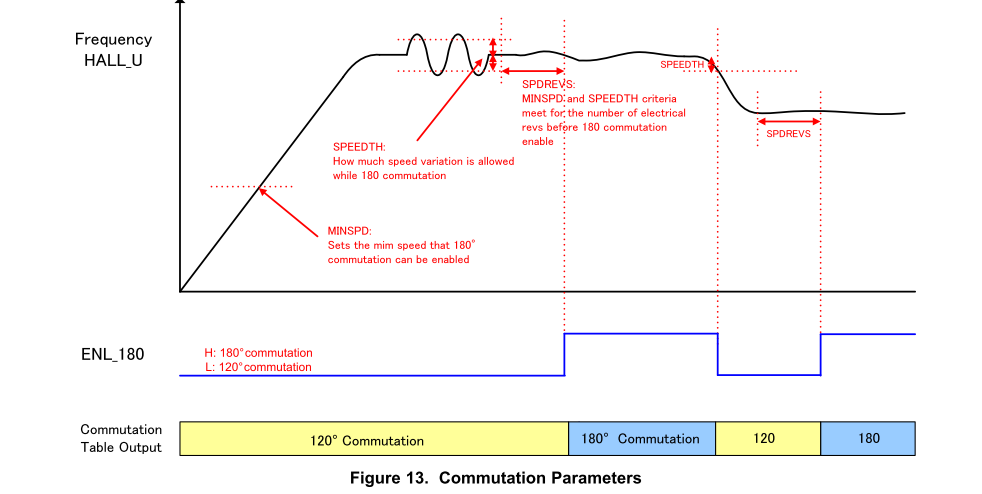

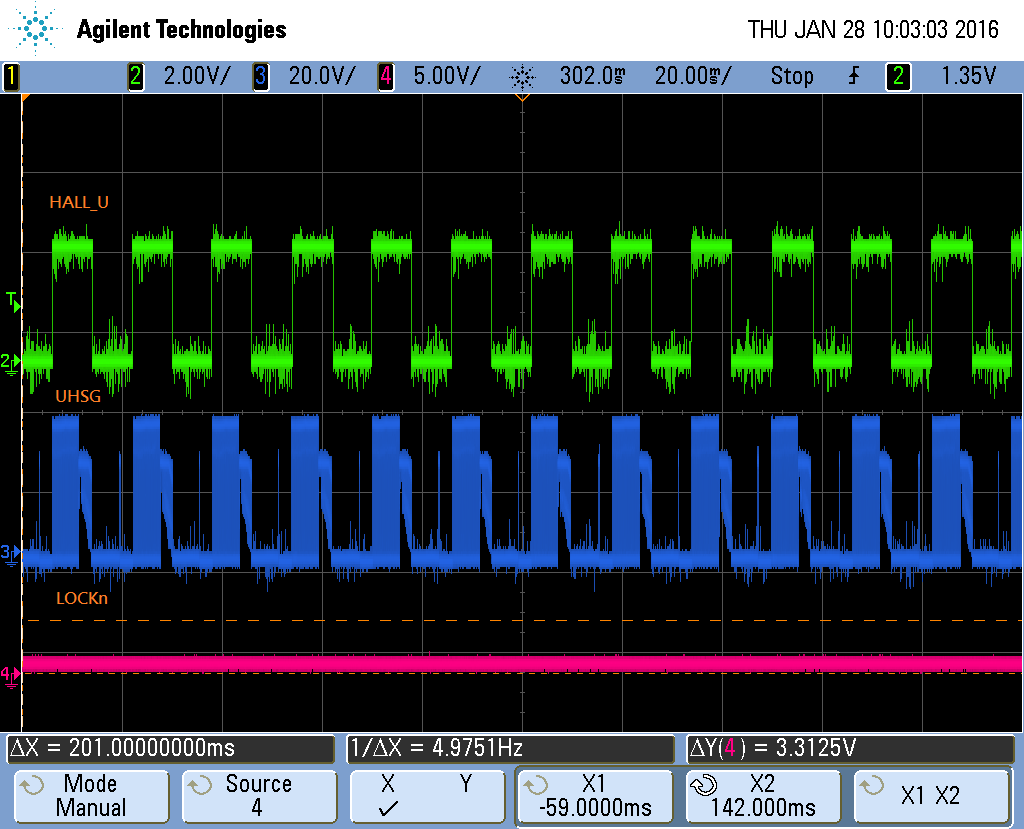

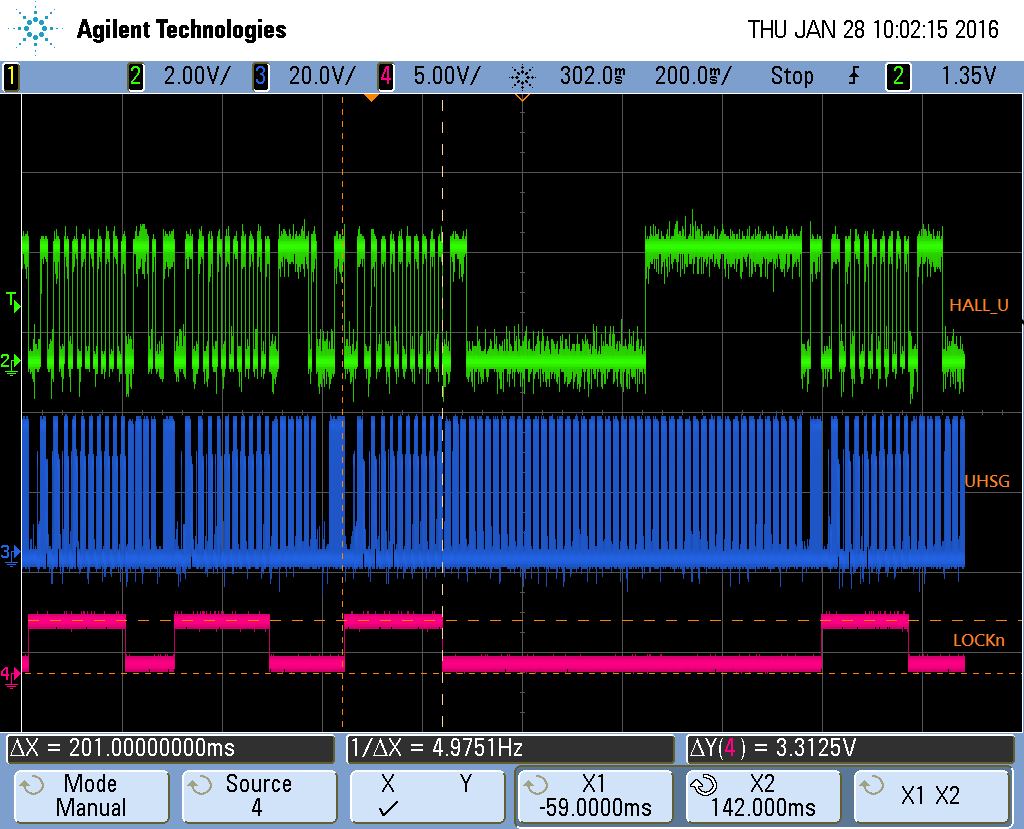

Question 2, while use register mode, the ENL_180 of 120 communication can let LOCKn to low. But while speed fixed and change to 180 communication, the LOCKn is not stable. Has any problem? Thank you.