Hi there,

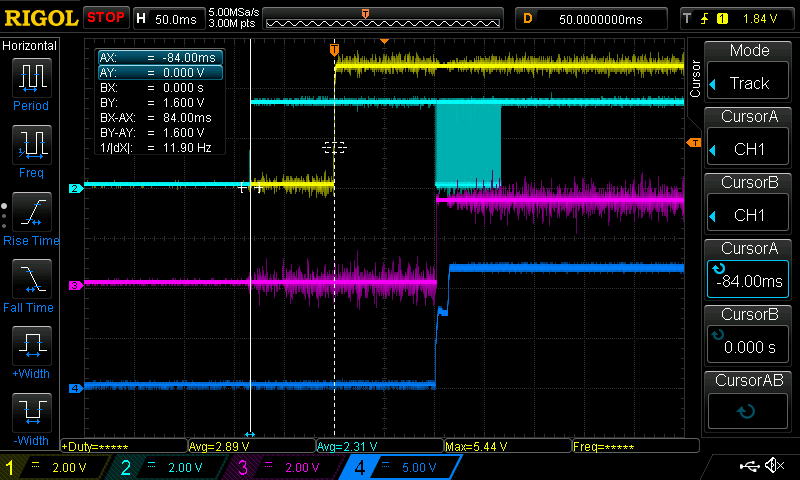

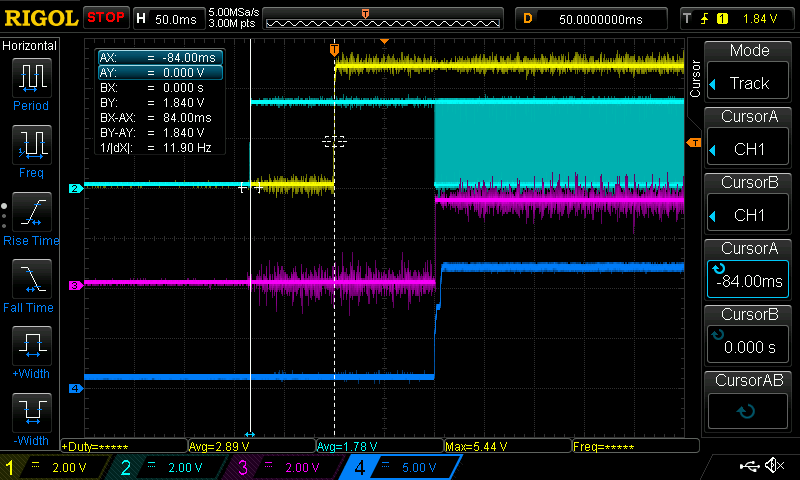

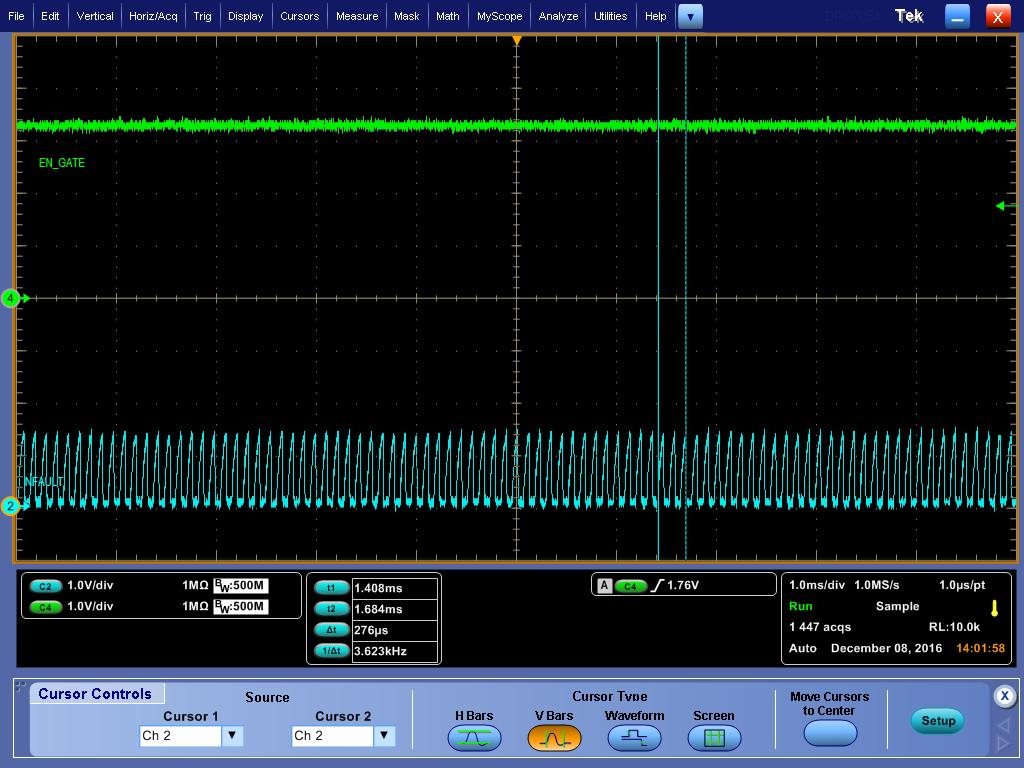

As mentioned in title, nFault pin of DRV83053 pulls low in random occasions, without any report of fault on SPI. The chip can still drive a load properly.

When nFault is released, it functions properly after a few power cycles, and reports faults correctly due to low voltage and such. So the pin seems functional. It appears like it latches down occasionally without an apparent issue.

- This is the first time we see this happening.

- I confirmed that it is in fact DRV8305 holding the pin low. There is a 100 ohm resistor between this pin and micro controller. In normal conditions, the voltage levels on the pin (high or low) are normal. But when it latches low, I have tried to short the micro side of the 100 Ohm resistor to 3.3V supply, and the DRV8305 side of 100 Ohm remains close to 1V, indicating the chip is pulling it down.

- On the micro controller side, we have a 4.7k pull up resistor. We have the same circuit on the power good pin that works normally without any latching.

Thank you,

Mehdi