Other Parts Discussed in Thread: DRV8303, CONTROLSUITE

Hello,

We use the DRV8303 EVM board to drive an BLDC motor. We measure the bridge current with the circuit that is already on the board.

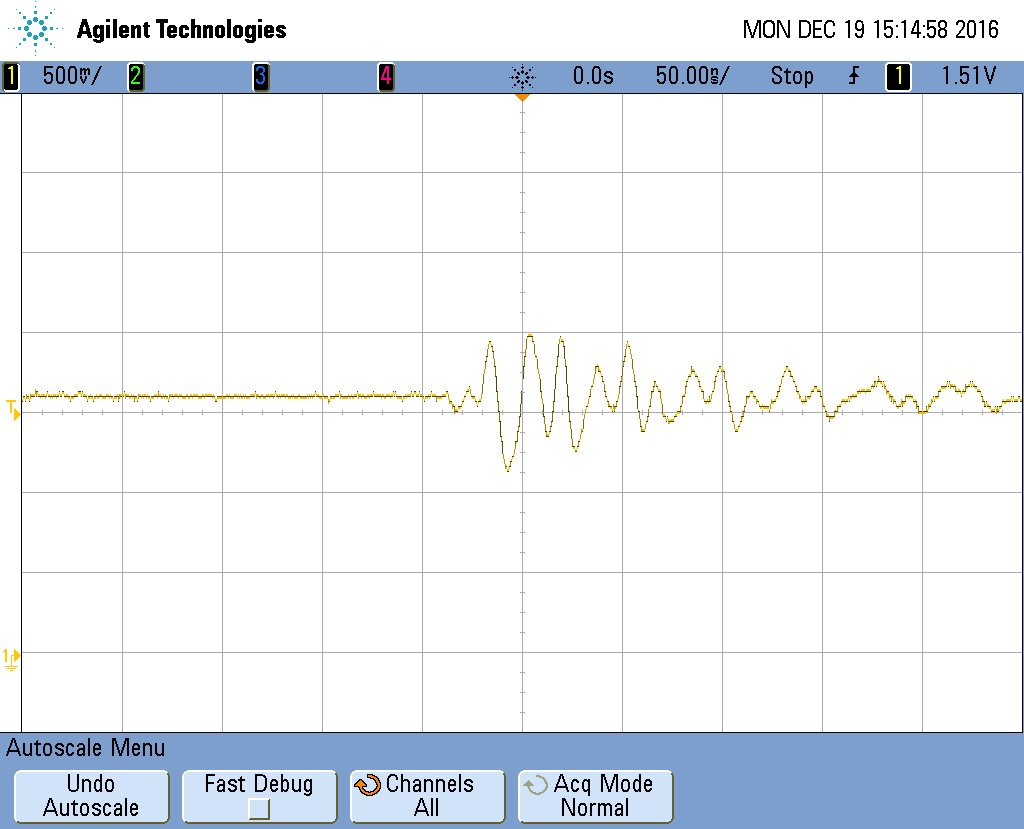

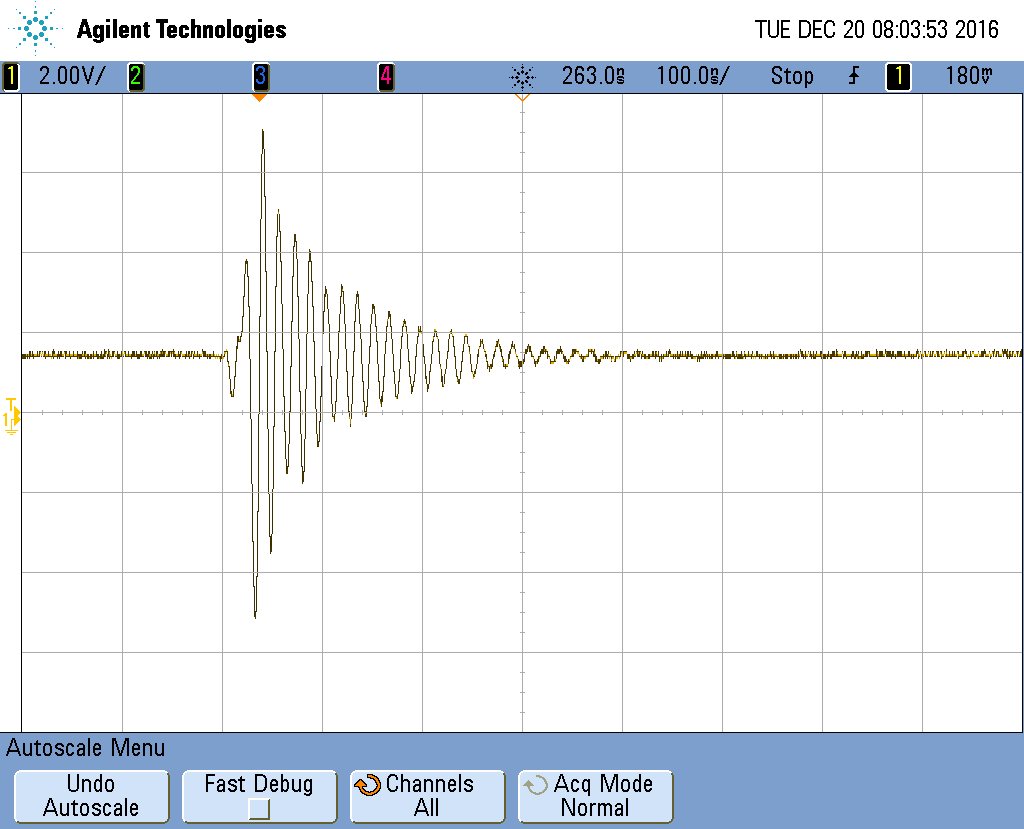

We have got a problem by measuring the current. If the PWM signal for the gate of the MOSFET is set, we can measure a interfering signal that seems to be an EMC problem.

The voltage we measure on the output of the differential amplifier (available on the drv8303 evm board) should be nearly 1.65V. If we switch a MOSFET for a certain time, we measure a ripple with an amplitude of about 400mV between TP20 and TP19 (for example).

We also can measure the interfering signal between to analog ground pins, described with TP19 and TP17 on the schematic of the DRV8303 EVM. Due to this fact we think that it is an EMC problem because we also have the interfering signal on the ground plane.

What can we do to decrease the amplitude of the interfering signal? Without changing layout and if we have to change the layout have you got some suggestions how?

(Have you got any EMC measurement data for this device? )

Thank you,

Florian