Hi BU team

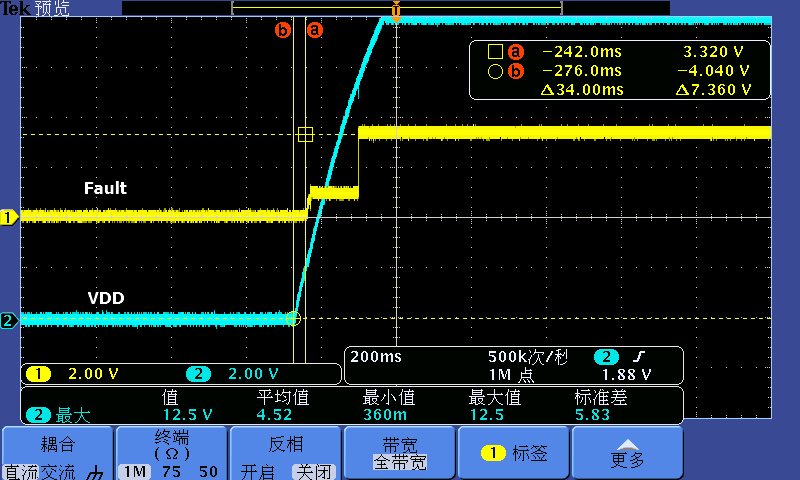

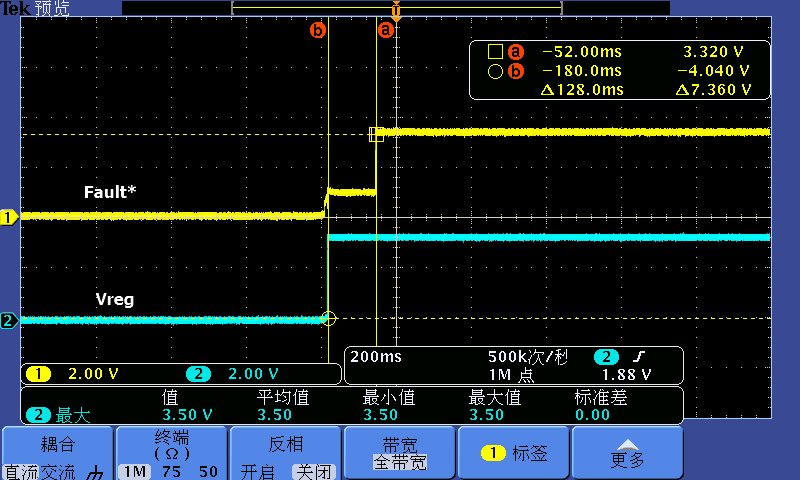

DRV8412 was designed for the stepper motor application. Monitored the Fault* pin timing during the powered-up and found an unsmooth rising edge.

The issues were showed in two below screenshots.

Would you help check it and share your comments?

Thanks