We are using a 77W 8-pole BLDC with the DRV8308. Our application is a small outdoor vehicle which will hold up to 20kg. The starting speed must be very slow (around 1km/h).

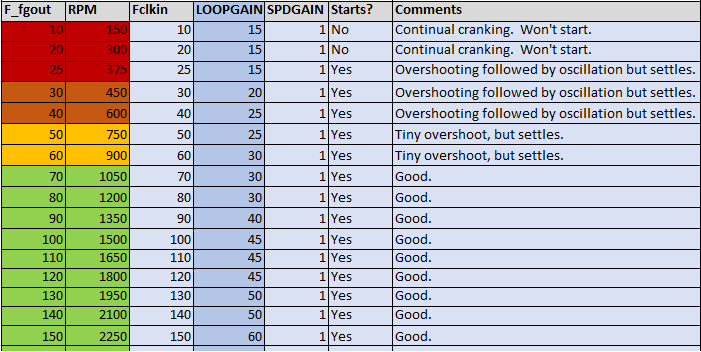

Using the DRV8308 EVM and our own PCB, we are unable to get closed-loop to get a solid LOCKn at any speed lower than 60Hz.

60Hz translates to around 1.2km/h on our vehicle, but going from 0Hz straight to 60Hz results in a very sudden jerking motion. If we choose any speed lower than 60Hz (eg. 30Hz) we get shuddering/stuttering in the BLDC, and it's very hard to regain control (have have to choose a target speed of >100Hz to regain control).

What can we do to get the DRV8308 to obtain a lock at low speeds?

Thanks so much for your help.