Other Parts Discussed in Thread: DRV8305

Dear all

I am using an BOOSTXL-DRV8305EVM-Evaluation board together with a Particle Photon, 120 MHz-Microcontroller (3.3V).

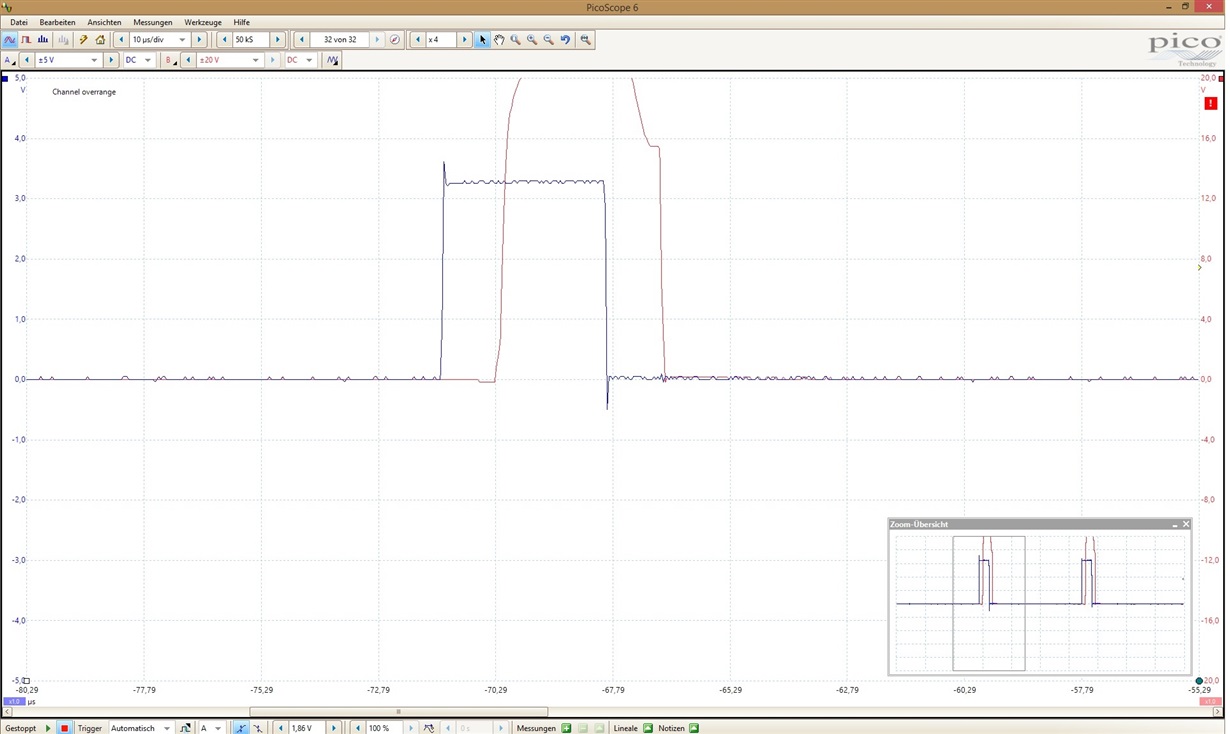

I configured the DRV8305 via SPI to 3-PWM-Mode in a open loop mode. For that, I give out a three sine PWM signals generated from a lookup table. PWM frequency: 28 kHz; Resolution 11 bit.

PVDD is 15V, the motor has an internal resistance of 0.3 Ohm.

As long as the duty cyle is high enough (appr. >10%), everything seems to work well. I can measure rising and falling Voltages from every Phase to ground. But I need a duty cycle of <1% that the motor doesn't burn at free wheeling at slow speeds (1 rpm). But with a duty cycle <10%, there are no voltages applied to the motor phases. Voltages from Phases to ground stays 0V. Either there is no error indicatet (red led on BOSSTXL isn't switched on).

What is the problem? Do I have to modify some configuration values?

Thanks a lot for your help.

Kind regards

Silvan

M.Sc.