Other Parts Discussed in Thread: TMS320F28377S

Tool/software: Code Composer Studio

I am using a DRV8301 gate driver and a TMS320F28377s MCU to control a BLDC motor.

When a fault is detected, the MCU reads the DRV8301 status register 1 to take appropriate action. The problem is that after an over-current condition, the DRV8301 only sets bit 10 which is a generic "fault" flag.

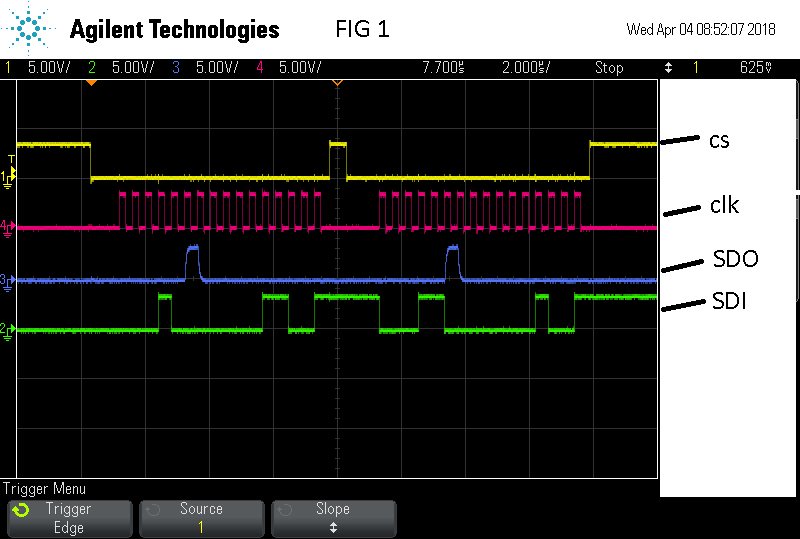

Please see Fig. 1 for SPI comms. scope capture immediately after an over-current fault.

It would be really useful if the appropriate bit indicating what type of fault has occurred was set. Can anyone advise why this is not happening?

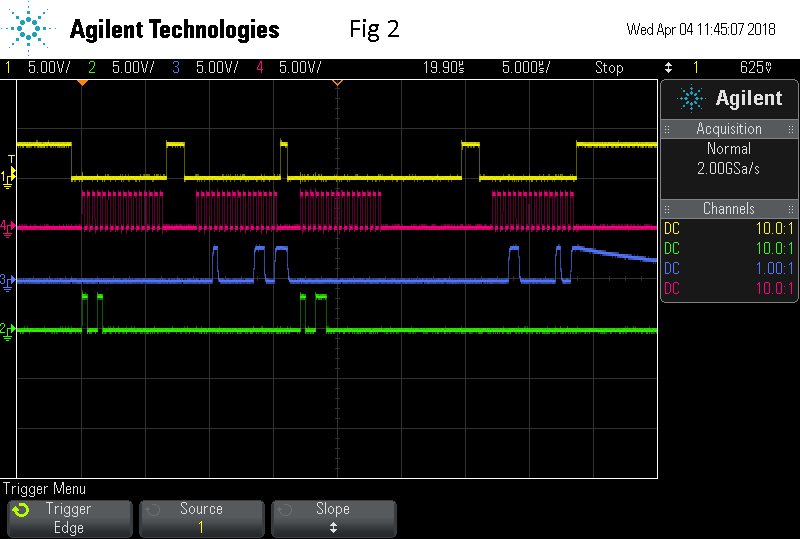

Please also see Fig. 2 for control registers SPI read capture.

Thanks,

Tony