Hi,

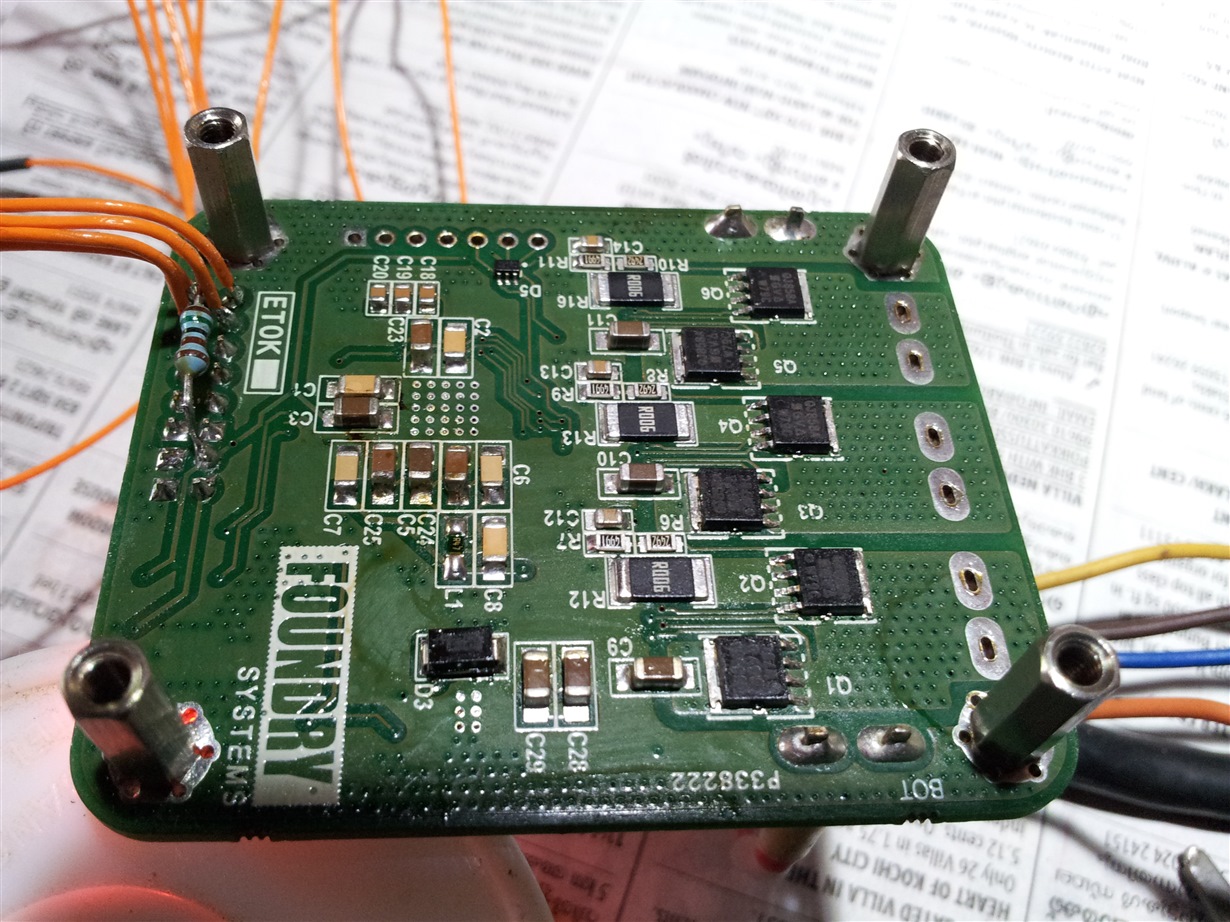

Have a DRV83053 connected over SPI to a STM32F334. Schematic attached. The SDO line had to be pulled by a 1k5 resistor, based on helpful feedback from here. Eventually, was able to get SPI communication working. Thanks to all those who helped.

Now, that SPI communications are okay. I am facing yet another issue:

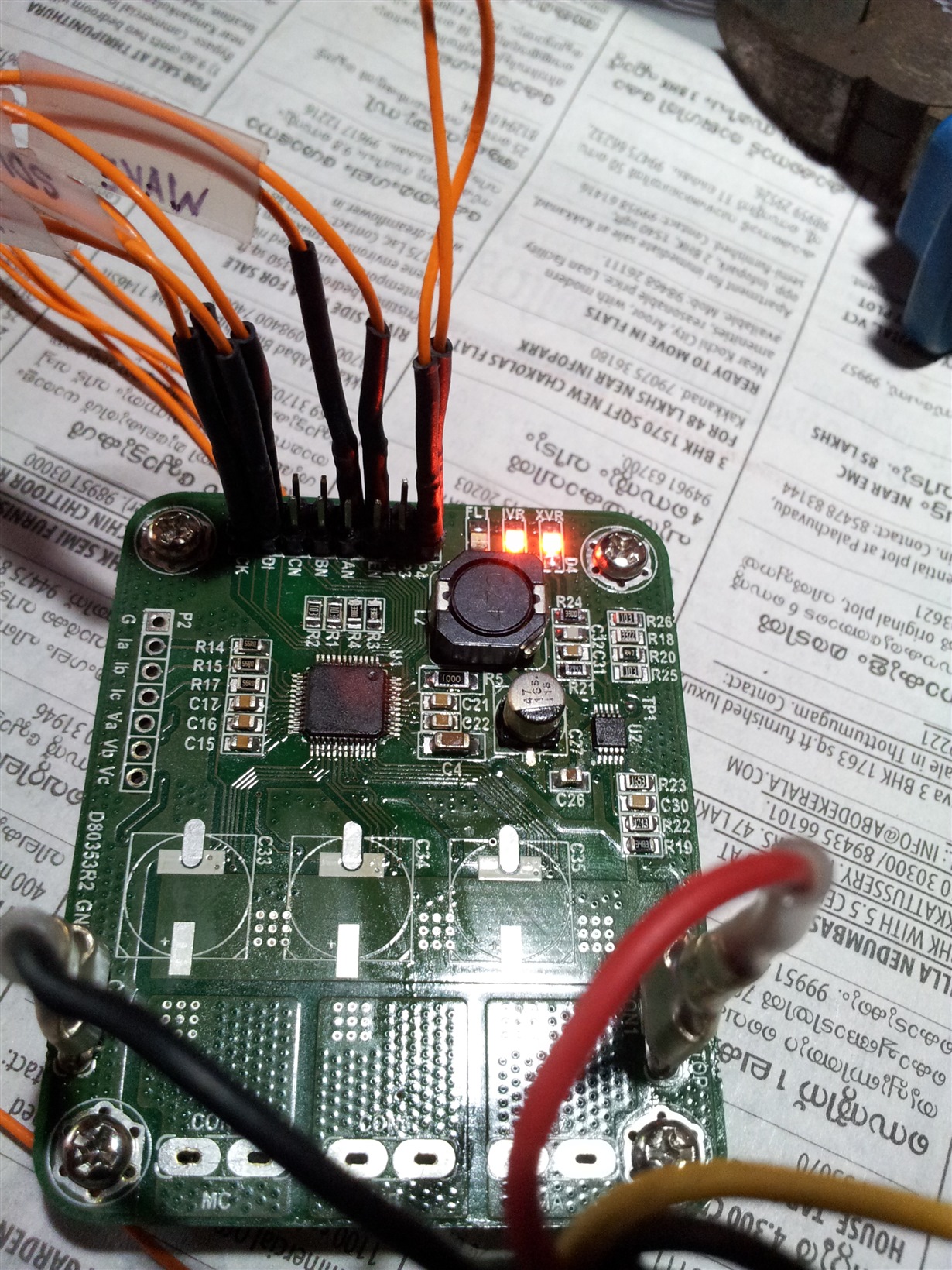

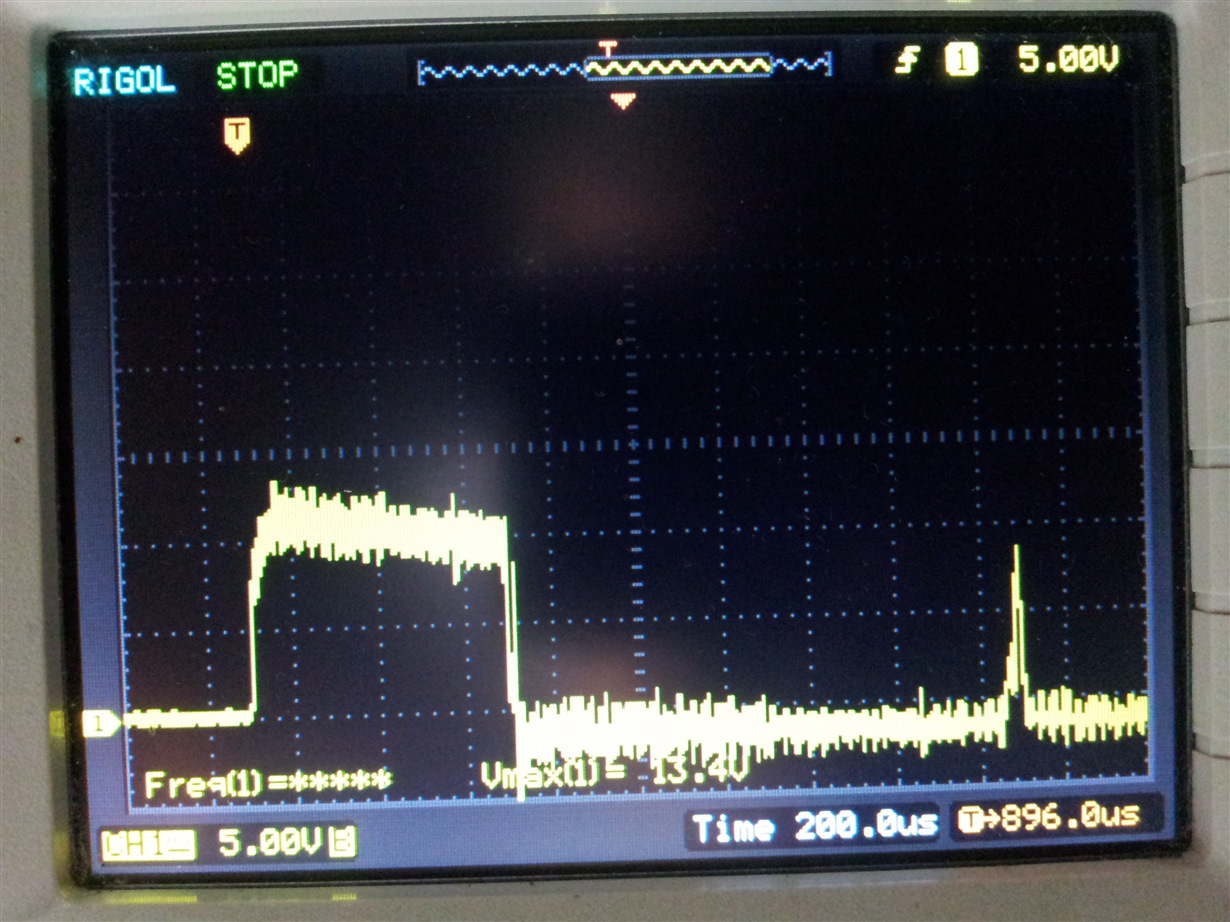

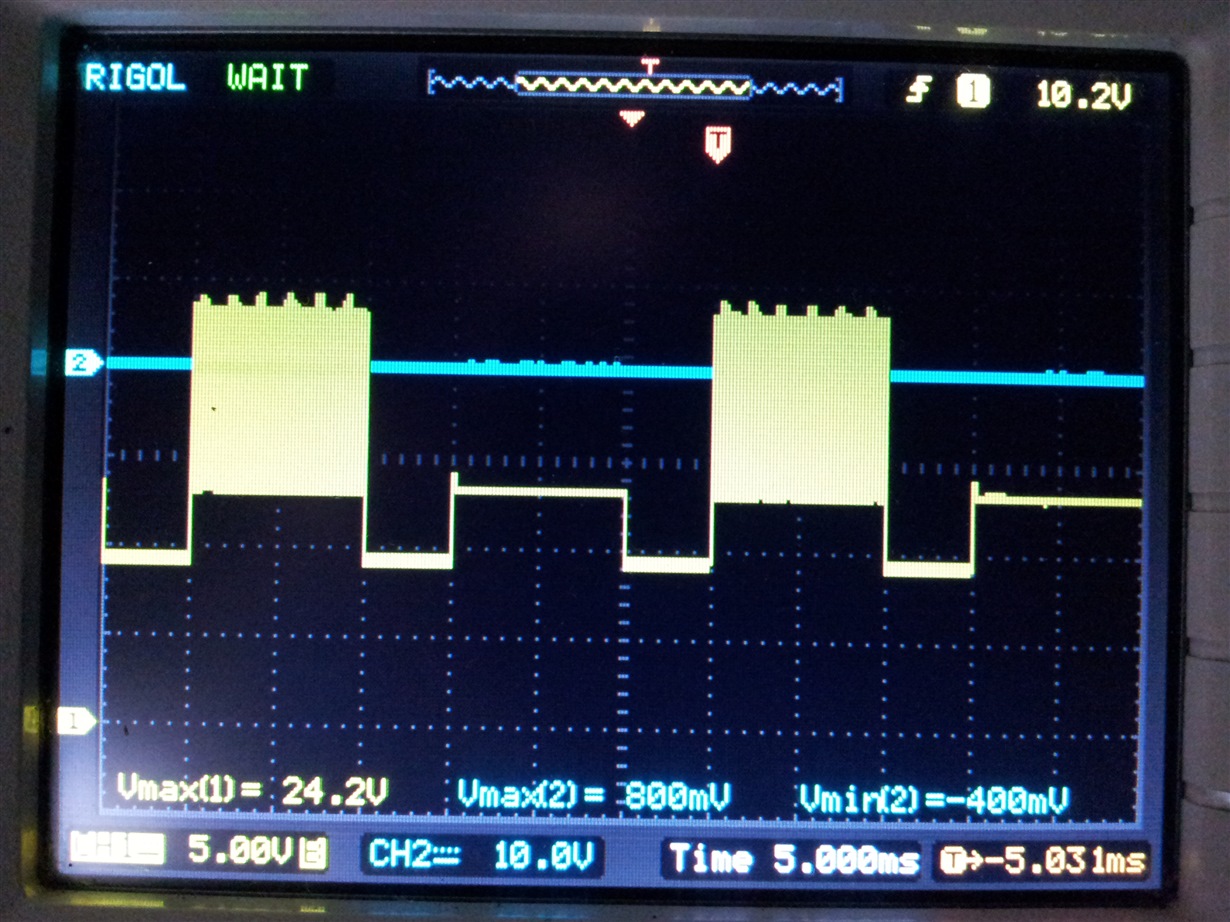

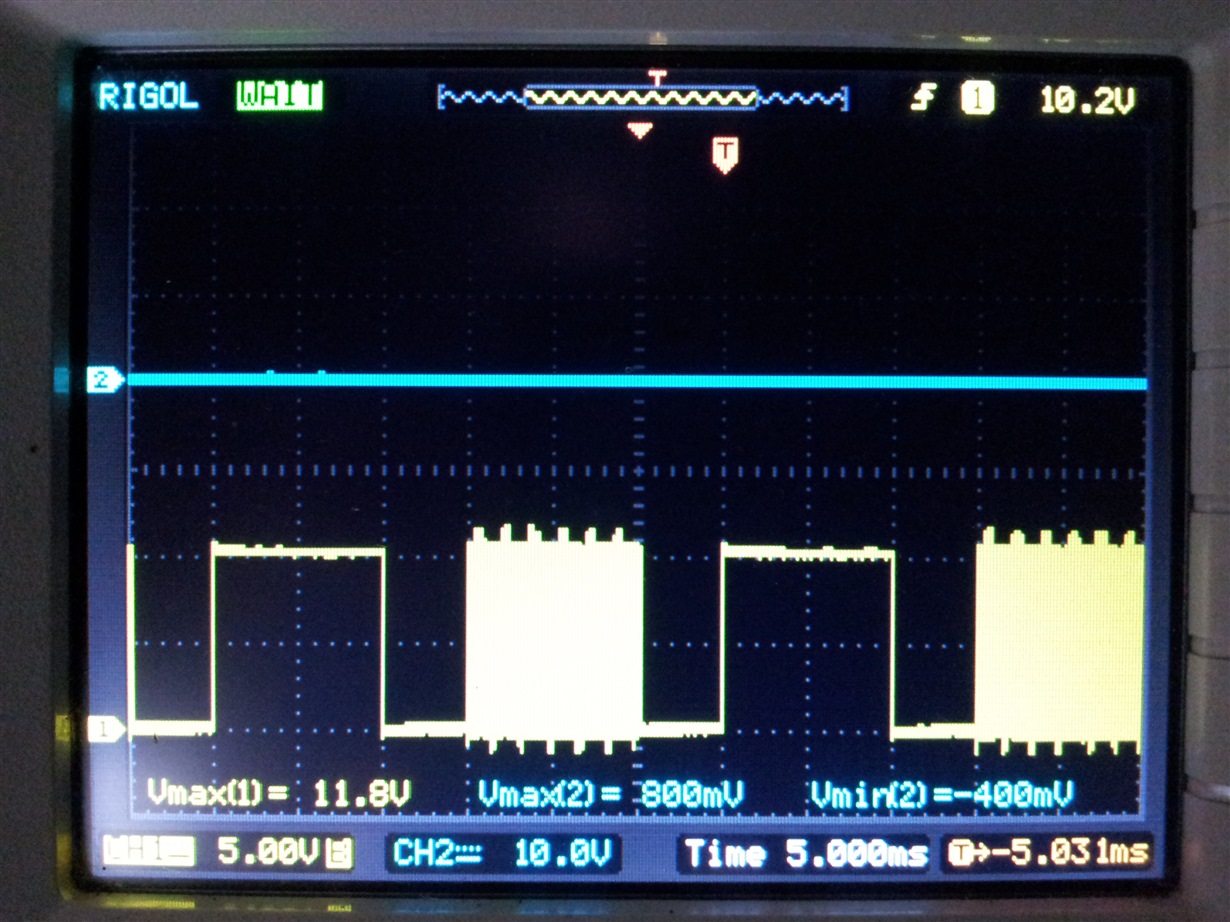

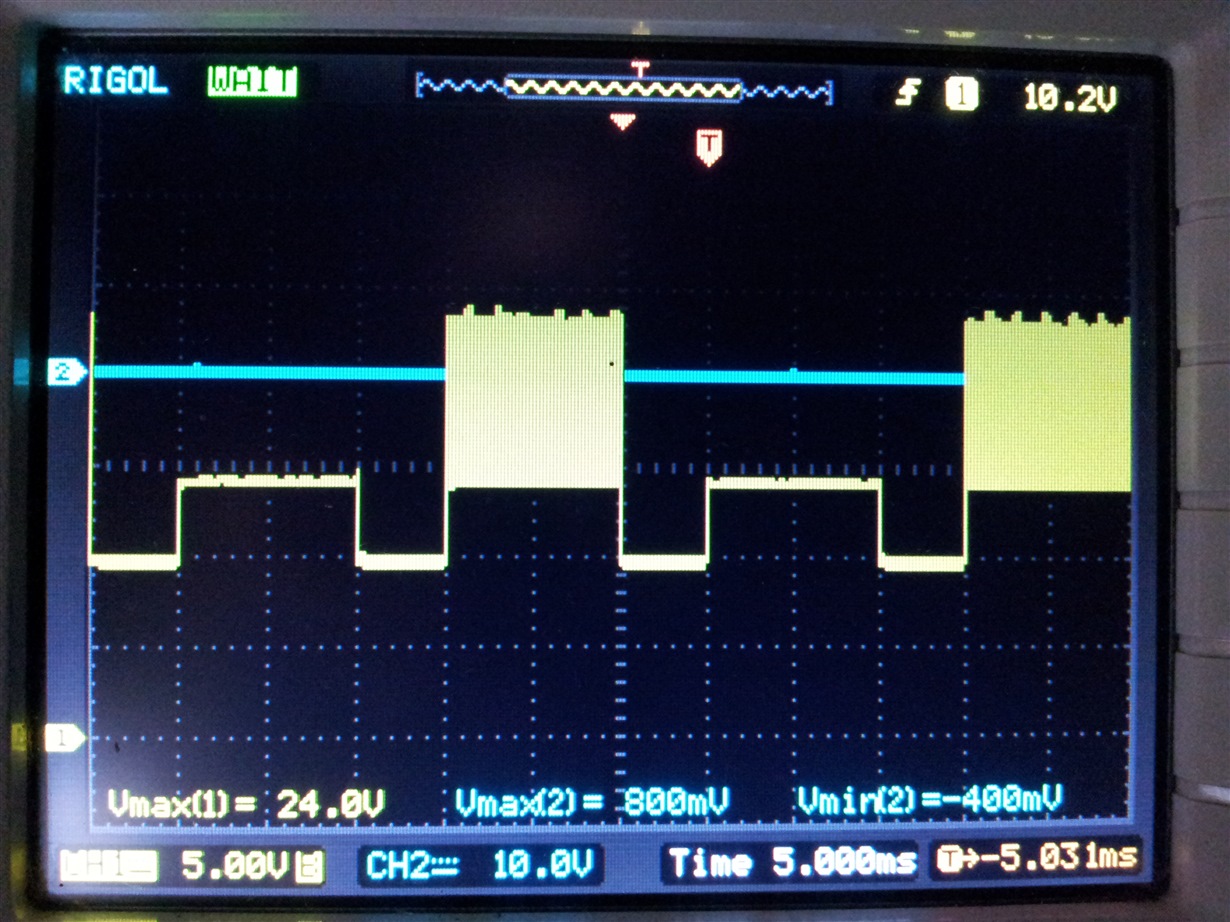

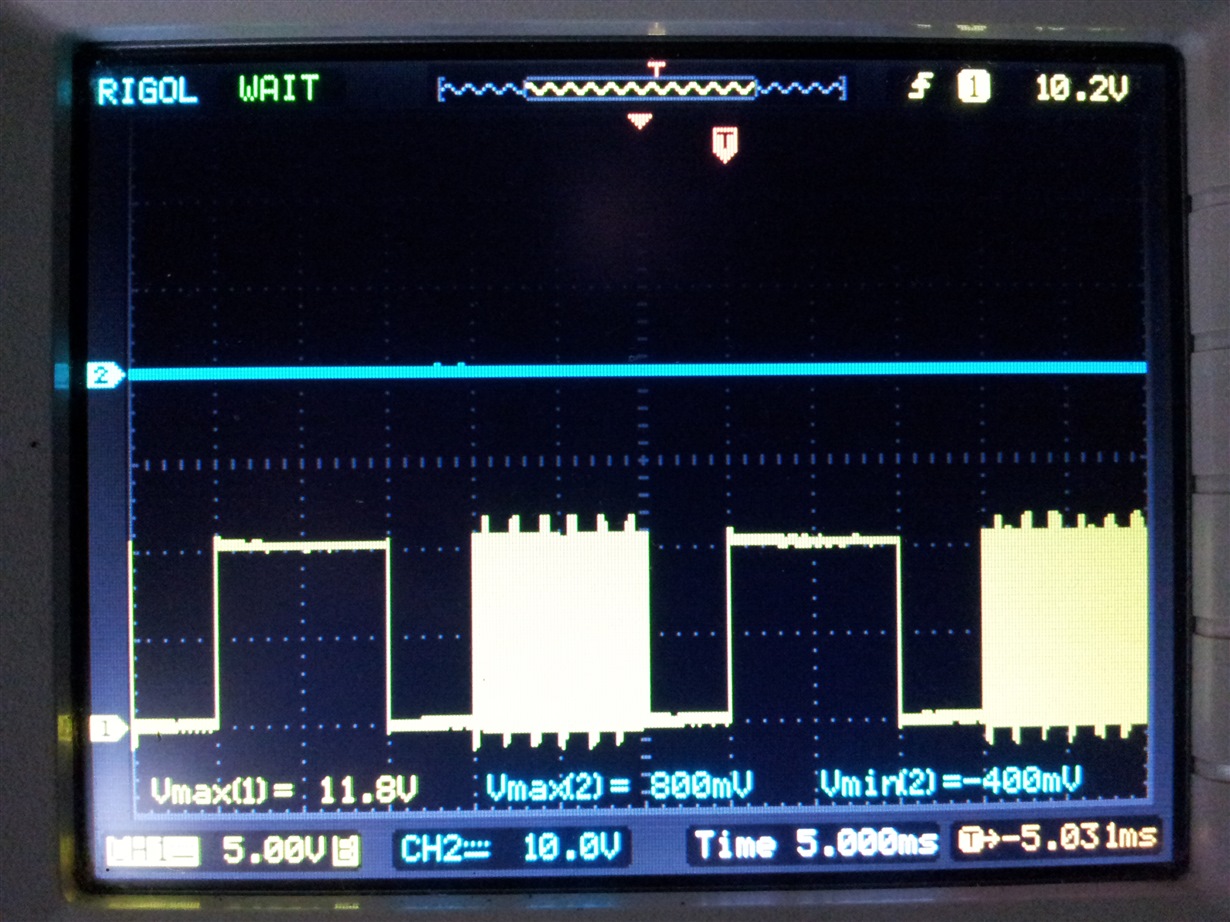

I am generating a PWM signal with the F334. I tried connecting that signal to INHA and provided EN_GATE from the microcontroller.

The moment, EN_GATE was pulled HIGH, nFAULT was raised.

At first, this issue existed with the 6-PWM independent mode. Tried 1-PWM and 3-PWM modes, but the results were the same.

A least in 3-PWM mode, the single PWM signal should not have been a problem ?

Is this the default behaviour of the DRV8305 ?

If yes, Is there a better way to test the functionality of the DRV8305 ?

The DRV8305 in initialized thus:

void drv8305_init(void)

{

static uint16_t reg_8305[13];

static uint16_t data;

uint8_t i;

/* initialize storage */

for (i = 1; i < 13; i++)

reg_8305[i] = 0;

/* read drv8305 registers */

for (i = 1; i < 13; i++) {

if (i == 0x08)

continue;

spi_read(i, &data);

reg_8305[i] = data;

}

reg_8305[0x05] = TDRIVEN_1780NS | IDRIVEN_HS_500MA | IDRIVEP_HS_500MA;

reg_8305[0x06] = TDRIVEP_1780NS | IDRIVEN_LS_500MA | IDRIVEP_HS_500MA;

reg_8305[0x07] = COMM_OPTION_ACTIVE_FW |\

PWM_MODE_3_INDEPENDENT |\

DEAD_TIME_35NS |\

TBLANK_0US |\

TVDS_2US;

reg_8305[0x09] = FLIP_OTS_ENABLE |\

DIS_VPVDD_UVLO2_DISABLE |\

DIS_GDRV_FAULT_ENABLE |\

EN_SNS_CLAMP_ENABLE |\

WD_DLY_20MS |\

DIS_SNS_OCP_ENABLE |\

WD_EN_DISABLE |\

SLEEP_AWAKE |\

CLR_FLTS_NORMAL |\

SET_VCPH_UV_4D9V;

reg_8305[0x0a] = DC_CAL_CH3_NORMAL |\

DC_CAL_CH2_NORMAL |\

DC_CAL_CH1_NORMAL |\

CS_BLANK_500NS |\

GAIN_CS3_10VV |\

GAIN_CS2_10VV |\

GAIN_CS1_40VV;

reg_8305[0x0b] = VREF_SCALING_K4 | SLEEP_DLY_10US | VREG_UV_LEVEL_10P;

reg_8305[0x0c] = VDS_LEVEL_0D123V | VDS_MODE_LATCH;

printf("\r");

for (i = 0x05; i < 13; i++) {

if (i == 8)

continue;

spi_write(i, reg_8305[i]);

}

printf("\r");

}

Initially, the SPI register Read write log, without the EN_GATE signal applied:

======================== STM32F334 Hello! ======================== DRV8305 Wake SPI Init: CPOL=0, CPHA=1, FRF=TI, LEN=16 -------------------------------- Read Reg1-12 -------------------------------- RD REG:0x01=0x00 RD REG:0x02=0x00 RD REG:0x03=0x00 RD REG:0x04=0x00 RD REG:0x05=0x389 RD REG:0x06=0x389 RD REG:0x07=0x281 RD REG:0x09=0x6a0 RD REG:0x0a=0x42 RD REG:0x0b=0x208 RD REG:0x0c=0x230 WR REG:0x05=0x389 WR REG:0x06=0x389 WR REG:0x07=0x281 WR REG:0x09=0x6a0 WR REG:0x0a=0x42 WR REG:0x0b=0x208 WR REG:0x0c=0x30 -------------------------------- Read Reg1-12 -------------------------------- RD REG:0x01=0x00 RD REG:0x02=0x00 RD REG:0x03=0x00 RD REG:0x04=0x00 RD REG:0x05=0x389 RD REG:0x06=0x389 RD REG:0x07=0x281 RD REG:0x09=0x6a0 RD REG:0x0a=0x42 RD REG:0x0b=0x208 RD REG:0x0c=0x230

The log after the EN_GATE signal is applied:

======================== STM32F334 Hello! ======================== DRV8305 Wake SPI Init: CPOL=0, CPHA=1, FRF=TI, LEN=16 -------------------------------- Read Reg1-12 -------------------------------- RD REG:0x01=0x420 RD REG:0x02=0x80 RD REG:0x03=0x00 RD REG:0x04=0x00 RD REG:0x05=0x389 RD REG:0x06=0x389 RD REG:0x07=0x281 RD REG:0x09=0x6a0 RD REG:0x0a=0x42 RD REG:0x0b=0x208 RD REG:0x0c=0x230 WR REG:0x05=0x389 WR REG:0x06=0x389 WR REG:0x07=0x281 WR REG:0x09=0x6a0 WR REG:0x0a=0x42 WR REG:0x0b=0x208 WR REG:0x0c=0x30 -------------------------------- Read Reg1-12 -------------------------------- RD REG:0x01=0x420 RD REG:0x02=0x80 RD REG:0x03=0x00 RD REG:0x04=0x00 RD REG:0x05=0x389 RD REG:0x06=0x389 RD REG:0x07=0x281 RD REG:0x09=0x6a0 RD REG:0x0a=0x42 RD REG:0x0b=0x208 RD REG:0x0c=0x230

Any idea, what causes the nFAULT ?

Thanks,

Manu