Hello!

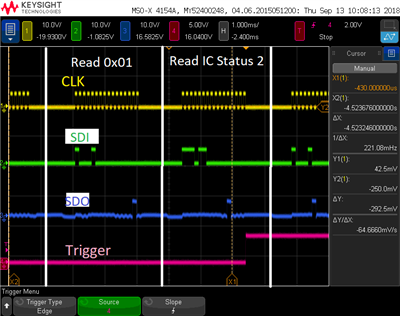

I have been helping a customer debug DRV3245 issues. They are seeing a SPI_clk_fault somewhat randomly. I asked them to rewrite the program so that it would read the 0x01 then read IC Status 2 register repeatedly until a fault occurs. When the IC Status 2 register changes a trigger happens (ch4) so that we can capture it on the oscope. In the picture below you can see that there was a SPI_CLK_FAULT triggered by the read of 0x01 but if you count the clock pulses there are 16 so doesnt seem like the fault should trigger...not to mention that the DRV3245 returns responses even though there is a supposed SPI fault.

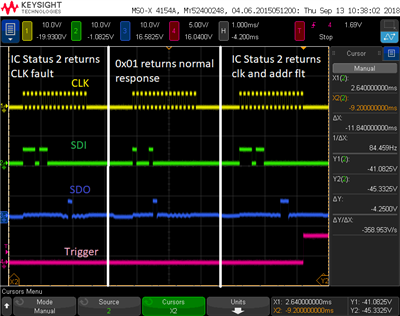

Then sometimes we see a SPI_ADDR_FAULT and SPI_CLK_FAULT occur like below. Again the DRV3245 returns with a response but the fault is triggered even though it looks the same as the other times the read occured:

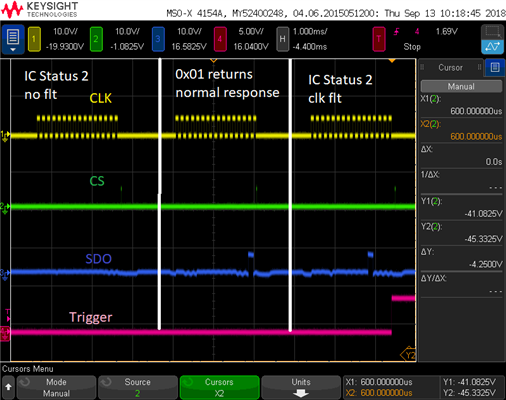

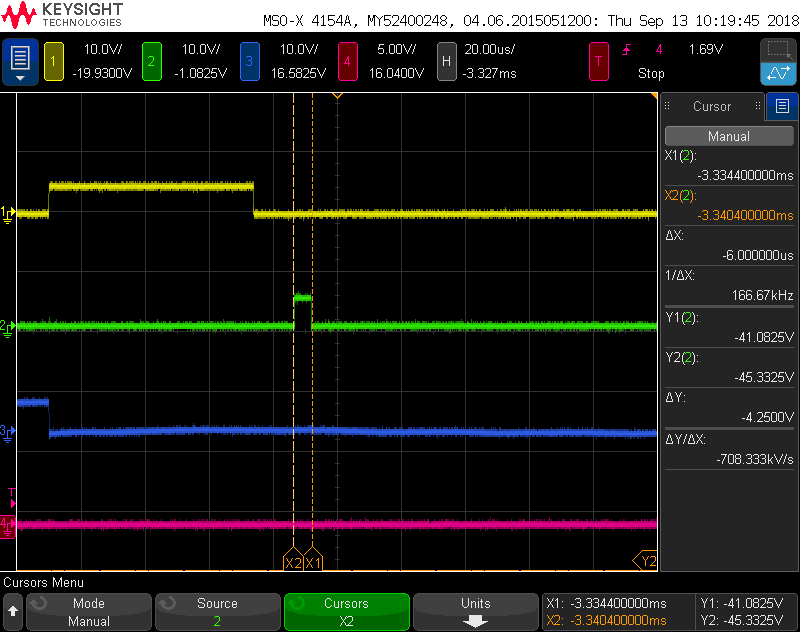

We also checked chip select to make sure there was nothing weird going on and that looks fine too. Two pictures below - first is zoomed out and the second is zoomed in on CS to check timing:

I'm out of guesses at this point it does seem to throw a fault randomly even though nothing looks wrong with the communication. Any guidance is appreciated!

Regards,

Kevin