Dear, Sir.

My customer is evaluating DRV83055QQ(Integrated 5V LDO) version.

Now, they are asking about the Power-Up Sequnce definition.

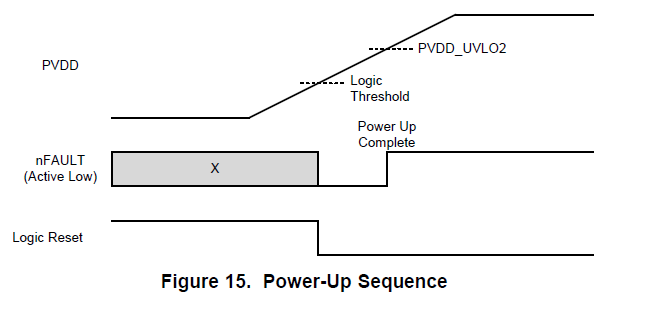

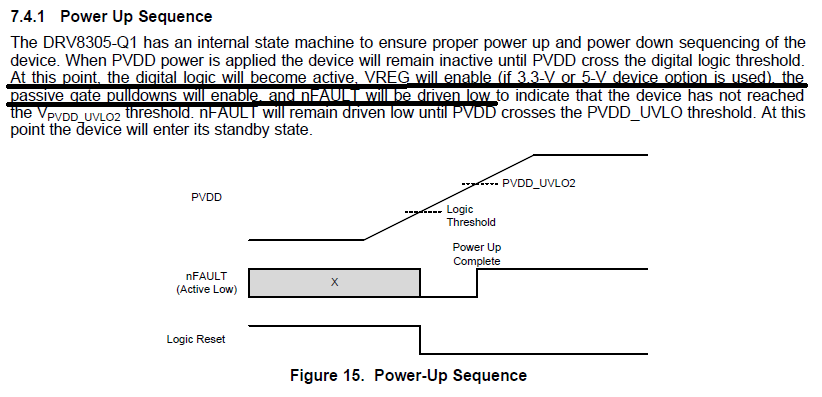

1. Figure 15 shows the definition. PVDD_UVLO2 is defined min. 4.4V/max. 4.7V @ rising.

How about the Logic Threshold? Digital I/O VIH = min. 2V/max. 5V?

2. Thecustomer is connected with 5V MCU via SPI. I think internal logic is operating with

3.3V. Is it no problmem to connect DRV83055QQ with 5V MCU? It has 5V tolerant?

Sorry again & again, but please give your advice.

Best Regards,

H. Sakai