Other Parts Discussed in Thread: TMS320F28377D

Hello,

We have a question regarding the SDO output characteristics of the DRV8320.

The datasheet is stating Td(SDO) SDO output delay time at 30ns.

Is that pure internal delay ie. time to drive the gate of the open drain internal mosfet or does it take into account the rise time outside of the component ?

We are asking this question as the datasheet does not provide the test conditions that led to the timing stated in the datasheet.

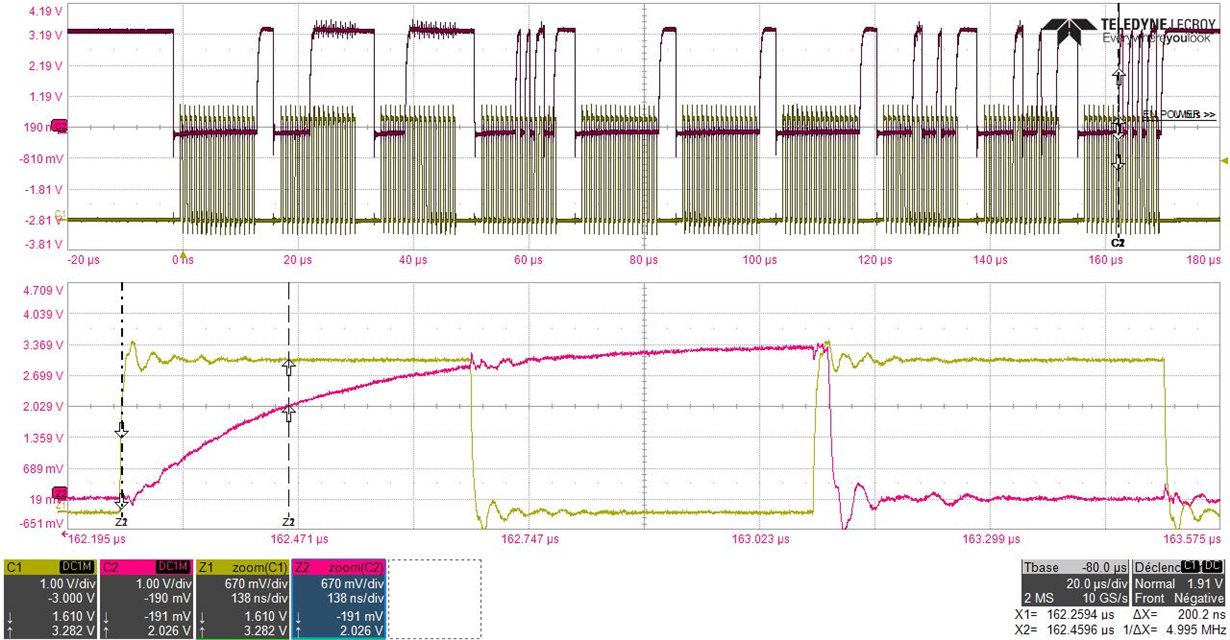

To ensure our design works, which was not the case at the beginning due to link frequency vs rise time, we did some tests with different pull-up values as highlighted in the below screenshots (don't pay attention to the labels, the yellow one is the clock and the purple one the sdo).

With a 4.99k:

With a 1k:

If the datasheet doesn't take into accout the rise time, it misses an information on the output capacitance of the DRV8320 which would allow us to compute it.

From our tests, we assume it's about 75pf/80pf (which is important compared to the TMS320F28377D input capacitance we have in front + the track capacitance).

Though we are able to have it working, I have concerns regarding min/max as we are performing our tests here at ambient temperature and we can't justify without further inputs from you our worst case analysis.

Best Regards,

Clément