Hi.

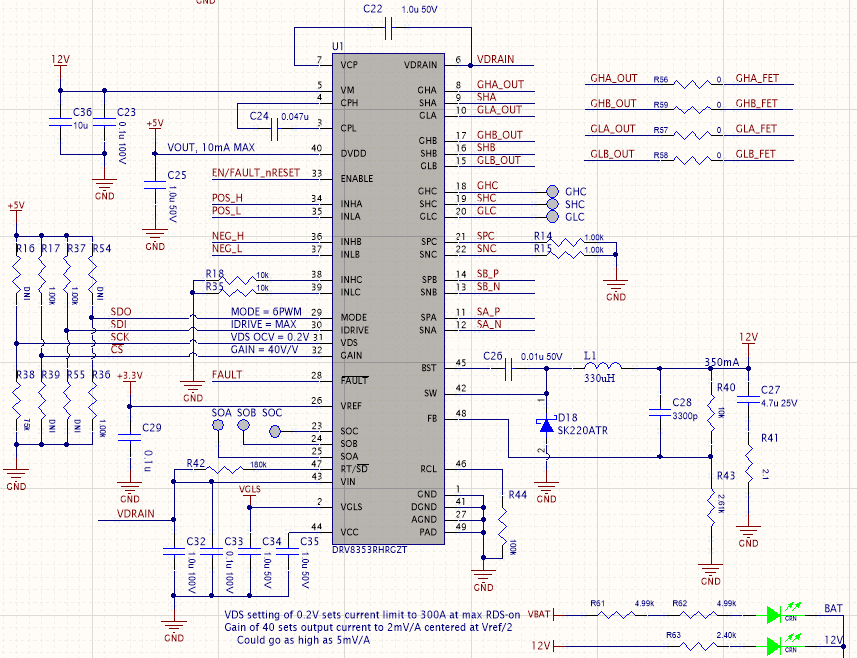

I'm having some trouble with the gate drivers on the DRV8353 failing after minimal use. Oddly, this is happening during bring-up with no-load or a small resistive load, reasonable voltages (14-24V); I haven't gotten anywhere close to the operating conditions.

I power up the bridge (slowly, by dialing up my bench supply from zero) and apply the logic reference voltage. Pull up the enable line, then manually toggle the INxy pins to ensure the bridge is being driven. After a few transitions, the FAULT line will assert and one of the Gxy will no longer be functioning (will always trigger the FAULT when I try to turn it on). Looking at the Gxy lines, the 'damaged' one will show an erroneous voltage in the off state (e.g. GLy will be > 0V when off) and the impedance to ground when unpowered will be much lower than the other channels and much lower than an undamaged board.

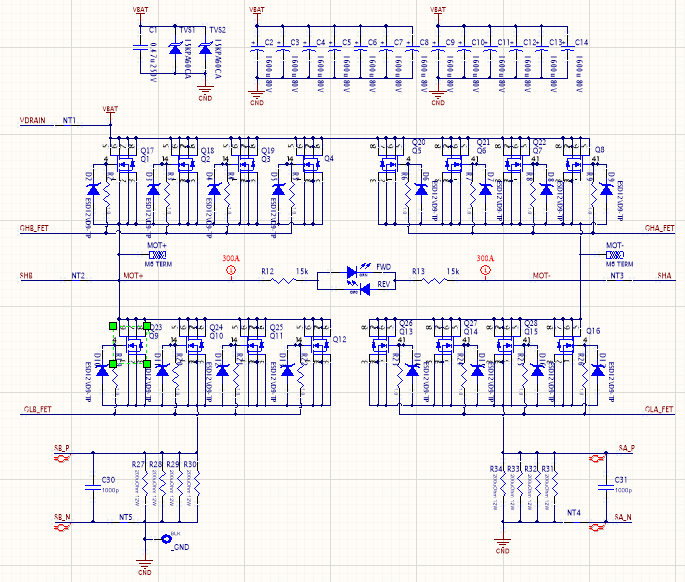

- I have isolated the H-bridge gates from the driver and found them all to be in good shape. I've damaged 3 boards now with two of the failures on low-side drivers and one on high-side.

- I have de-pop'd all but a single FET in each leg of the bridge, and seen the same effect. FETs are Toshiba TPH2R608NH,L1Q.

- Part is configured as 6 PWM, max drive, using the internal buck to create 12V which powers VM.

- The gate drive runs are long, but the GHy are reference to SHy, while the low side are ground (~SyP) referenced keeping the loop-area/inductance small.

- Gates are isolated each with a 1ohm resistor, and individually protected with a small TVS (theoretically providing some protection to the gate drivers as well)

I based the layout on the reference design and can't see any notable differences aside from the much larger bridge.

Any thoughts on what might be causing this would be greatly appreciated.

-Chris