Hi Team,

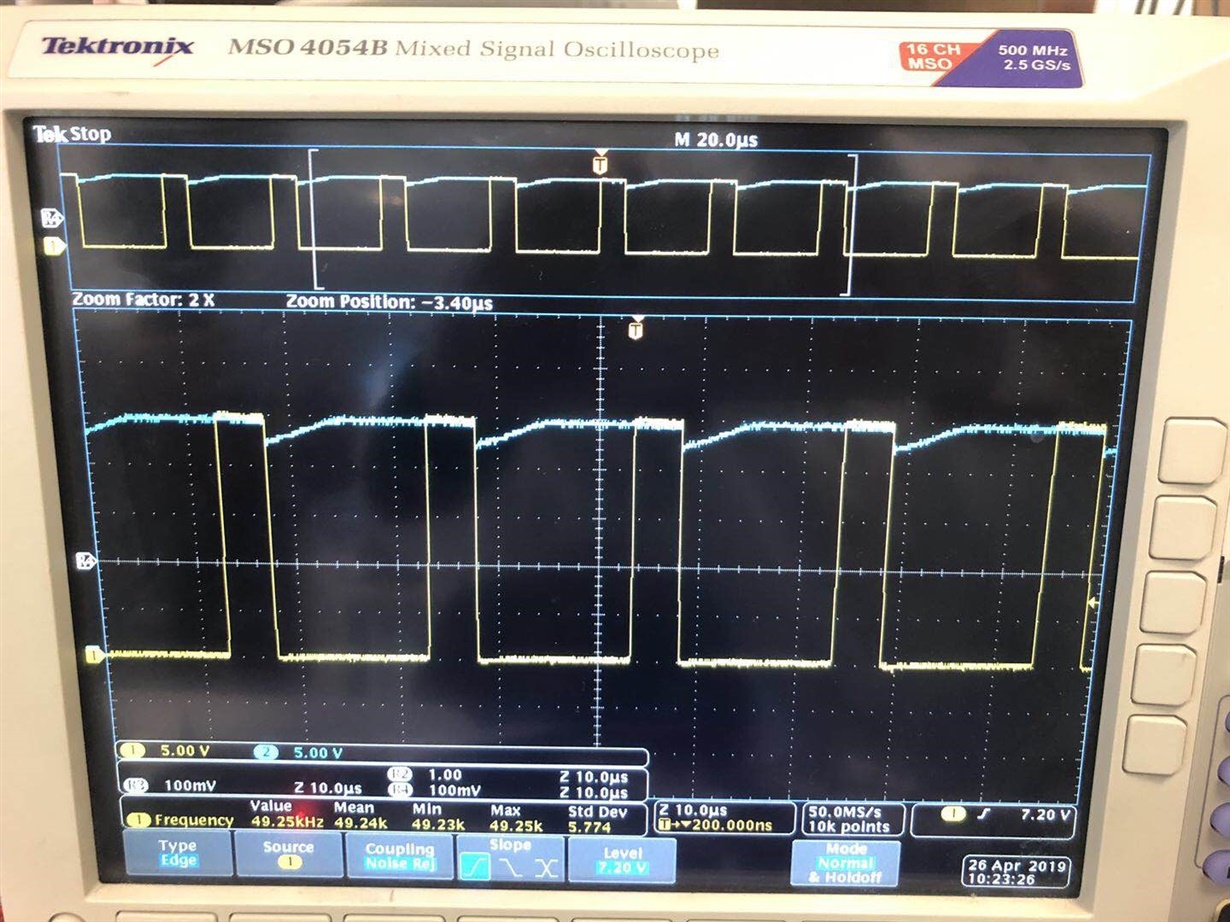

One of our customer has done some test with our DRV8860 on their prototype board (follow EVM circuit). DRV8860 is design to drive the valve. They have observed channel crosstalk when driving in one channel . In the below waveform, one channel is PWM switching, an adjacent channel is connected to a valve but in off state.

Can you help to comments what could possible lead to the 'dip' on the adjacent channel and any remedy we could try ?

Look forward to your feedback. Thanks in advance.