Hi, Team

Customer reported IC failure when doing outputs direct short test on DRV8844.

DRV8844 is plugged to +/-24V power supply and drive 4 bi-directional solenoids.

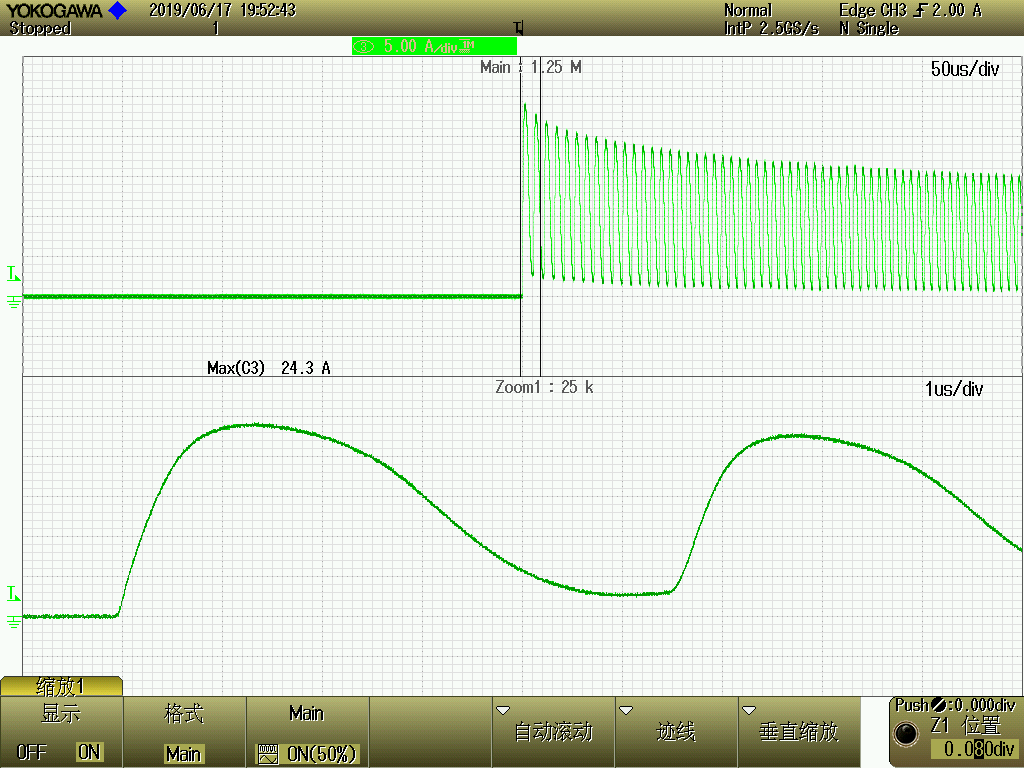

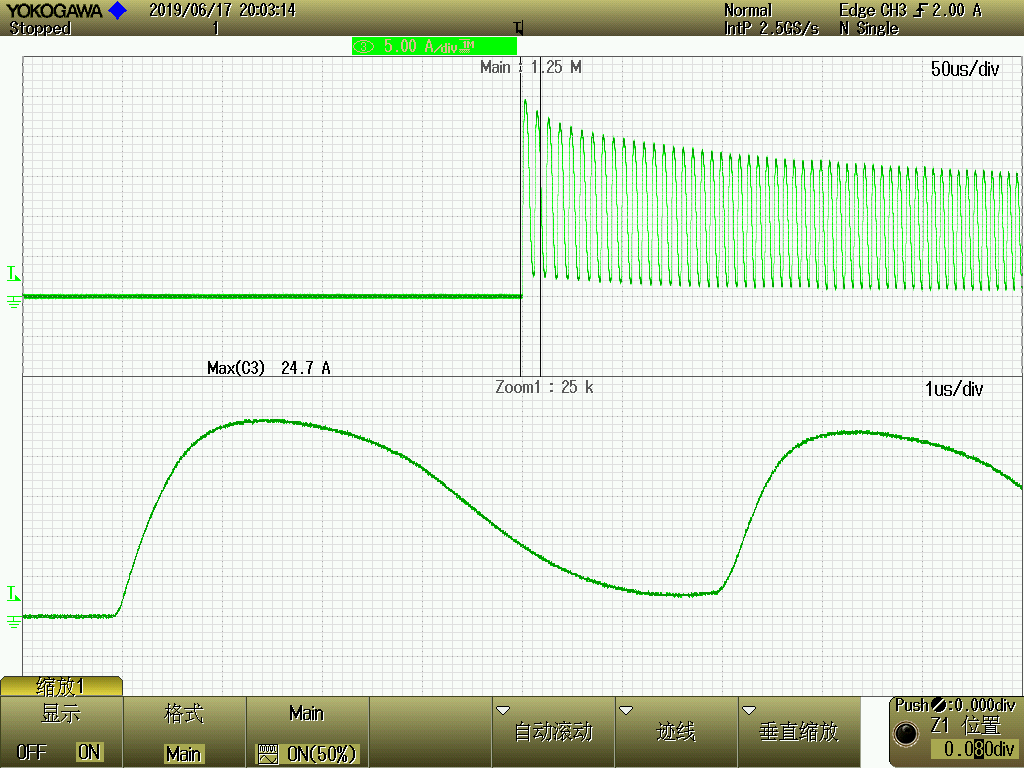

>20A peak current was captured from current waveform. IC was damaged. OCP not triggered.

Is there analog current limitation to avoid IC damage from inrush current?

Other than limit the current from power supply, any other suggestion we may offer to avoid failures?