Dear All,

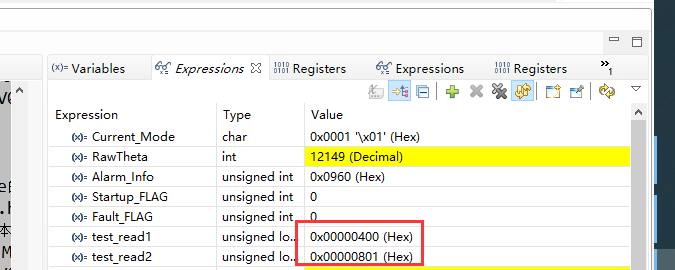

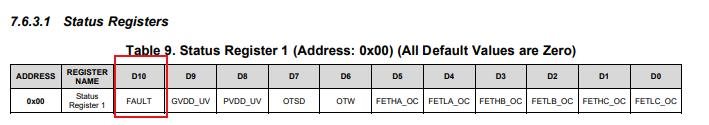

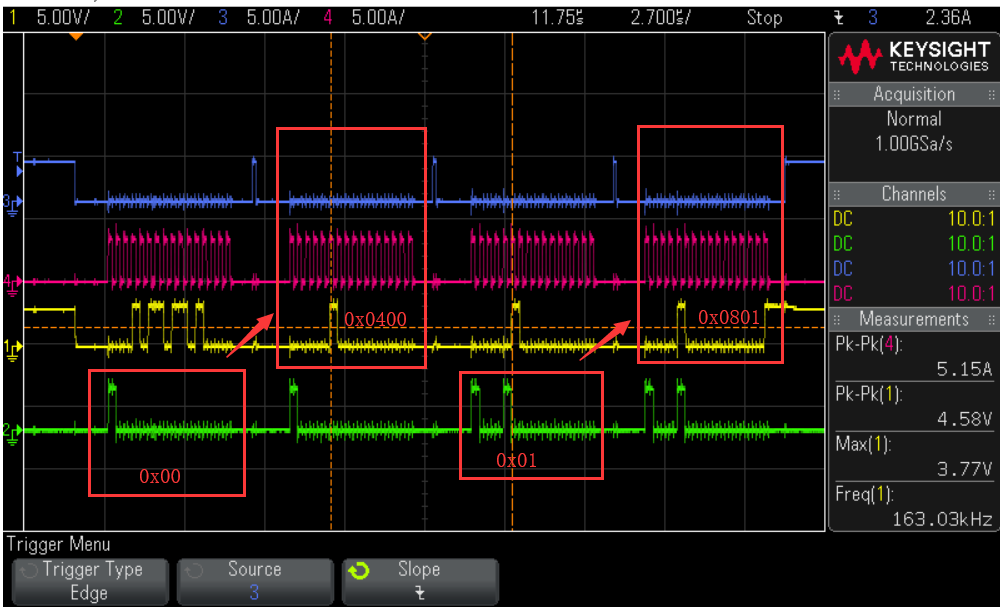

It is found that the error code of 0X0040 appears when using the driver chip DRV8301. The manual is not explained in detail. The error code location is as follows.

Please help explain what the meaning of D10 FAULT in the spec in 7.6.3.1 Status Registers?

How to solve this problem?

Thanks!