Dears,

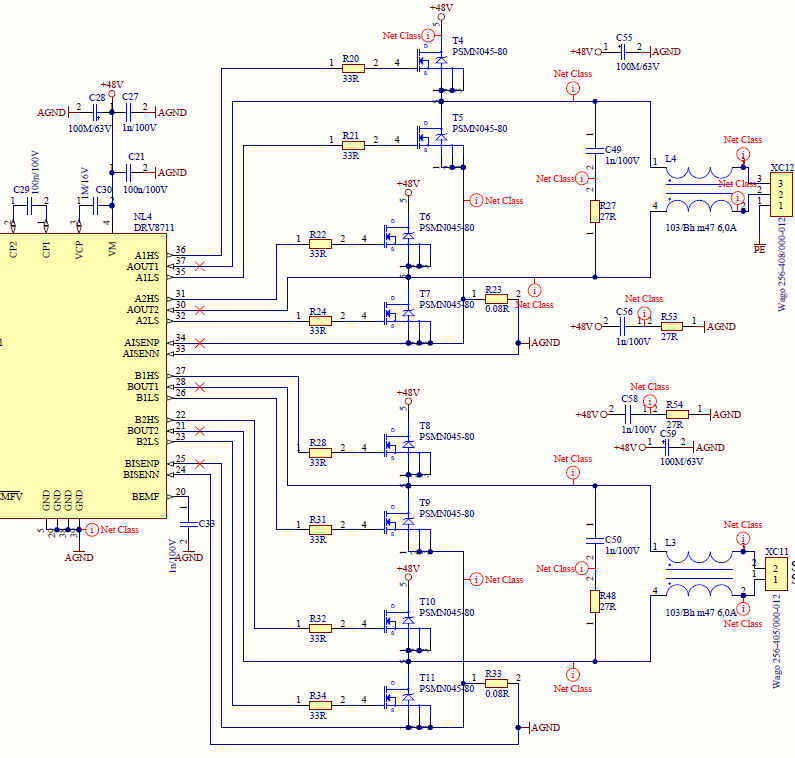

we use DRV8711 motor controller in our product.

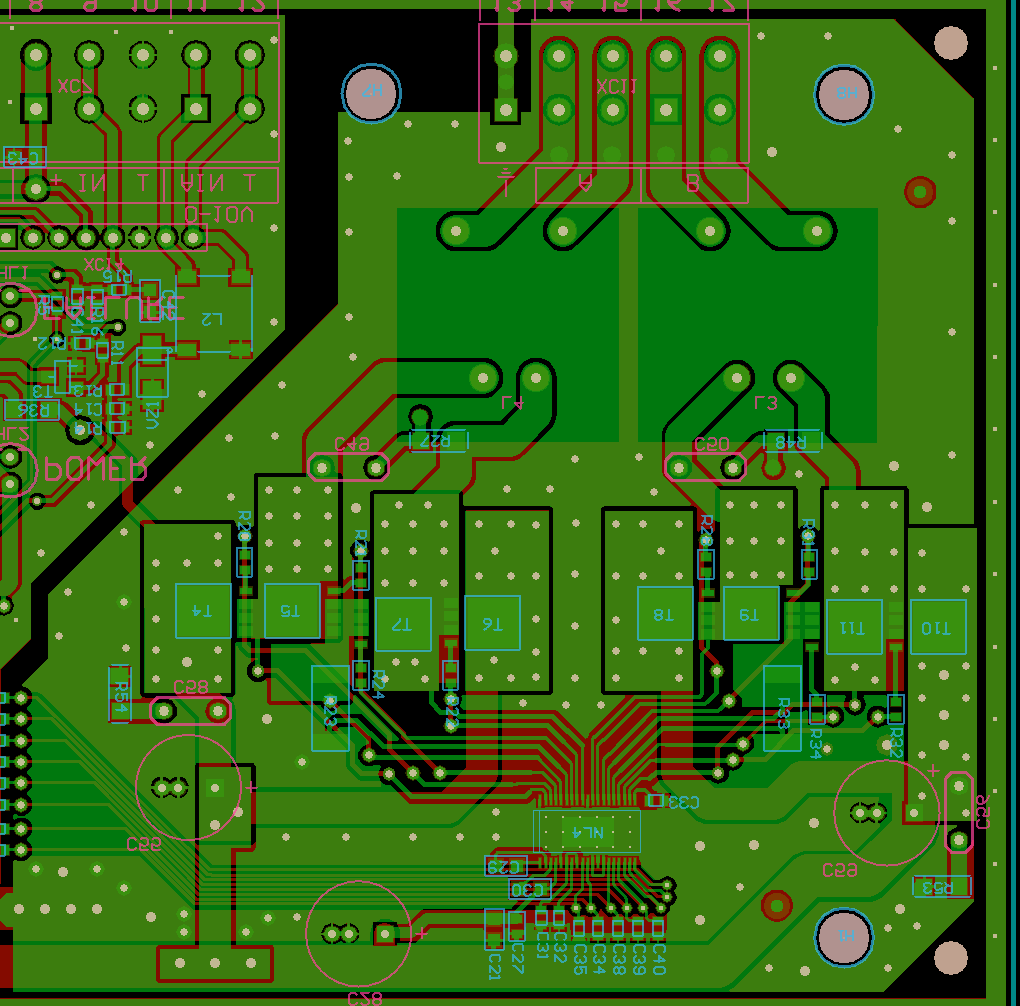

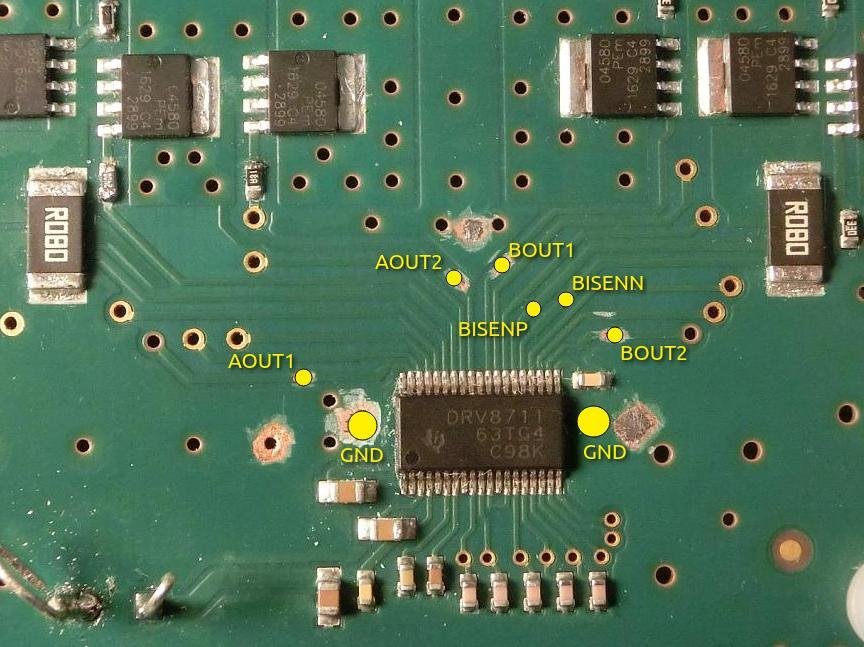

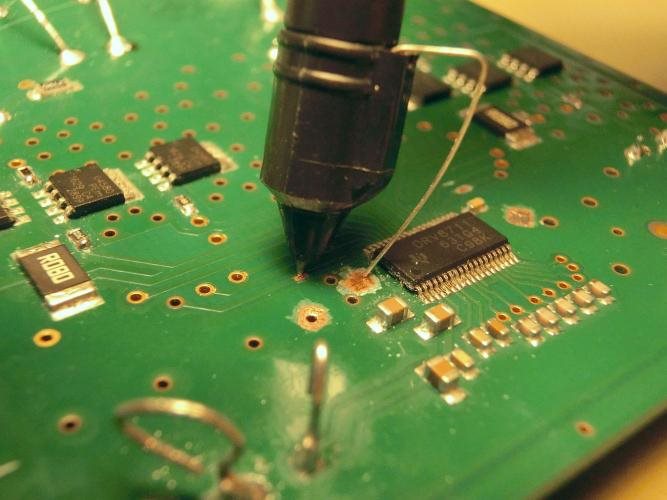

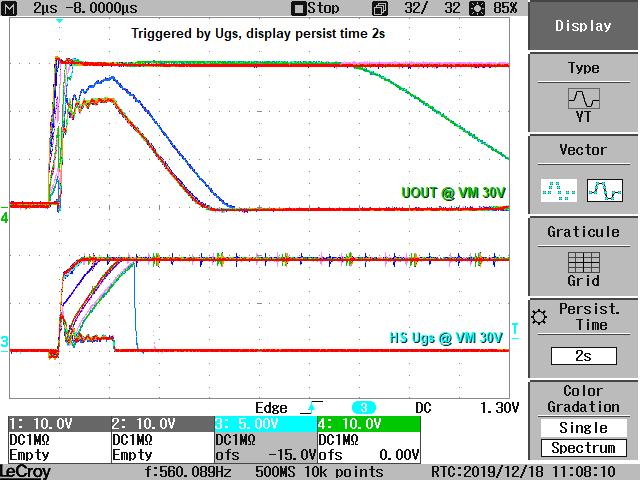

The product has a higher failure rate of DRV8711: the driver of the FET transtistor high side of the bridge is randomly damaged. Sometimes the one driver of HS transistor, sometimes three HS drivers, sometimes all four, are damaged on the controller. The damaged DRV8711 driver is not able to sufficiently open the FET high side of the bridge. As a result, there will be a large voltage drop on FET and the announcement of FAULT OCP. Everything works OK after replacing the DRV8711 controller. FET transistors are OK. Capacitors CP and VCP are OK. The power supply on the VM DRV8711 terminal is without voltage peaks.

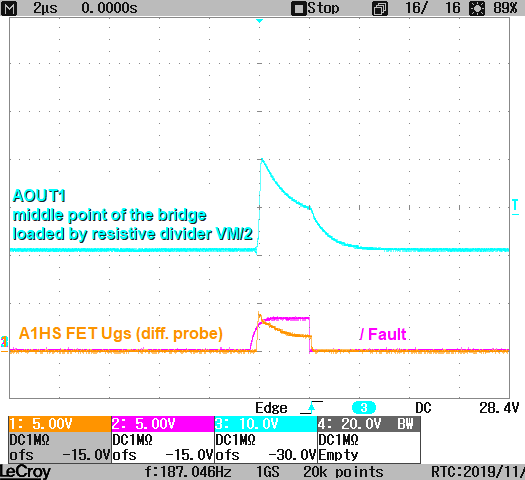

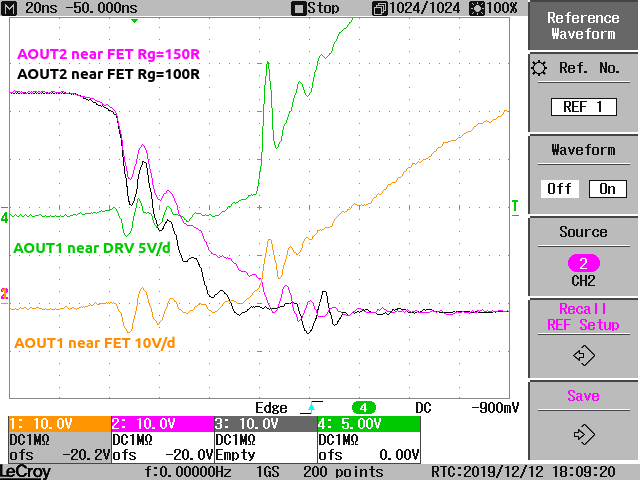

Picture output voltage of damaged driver A1HS:

Parameters of our application:

VM +44V

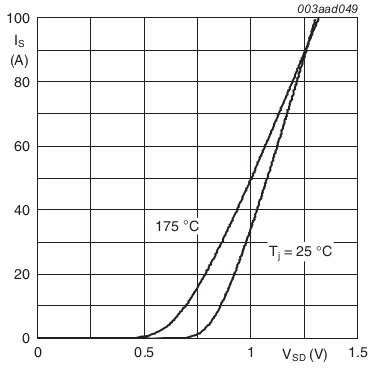

FET PSMN045-80 (gate-drain charge 3.1nC ; total gate charge 12.5 nC)

Rgate 33Ω

Rsense 80mΩ (Inductance less than 5 nH, BOURNS CRA2512-FZ-R080ELF)

Iout max. 3A

IDRIVEN 0x00 100 mA Low-side gate drive peak current

IDRIVEP 0x00 50 mA High-side gate drive peak current

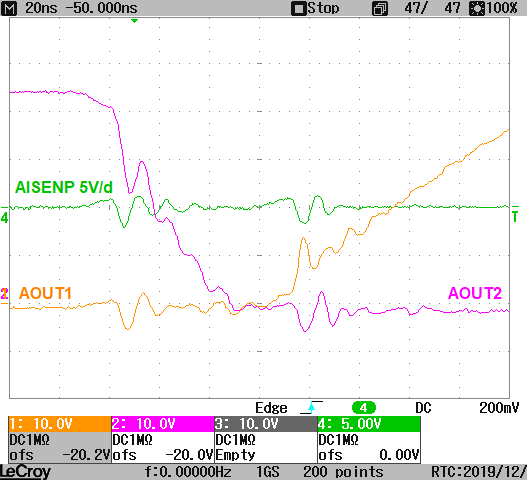

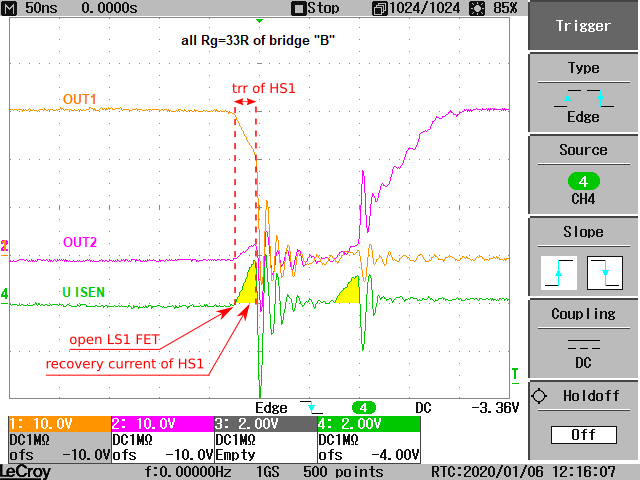

When we were looking for the cause, we checked the voltage waveforms on a good piece. On DRV8711 we measured very short negative peaks -5V / 10ns on AOUTx, BOUTx terminals and -2,5V / 10ns on AISENP, BISENP terminals.

Can these spikes cause the DRV8711 damage described above?

What else may be causing DRV8711 damage?

Thank you for your answer.

Michal