Other Parts Discussed in Thread: DRV832X

Hi,

I'm using DRV8323 for development.

The DRV832x family of devices are integrated gate drivers for three-phase applications,I want to know whether it can be applied to two-phase drive control

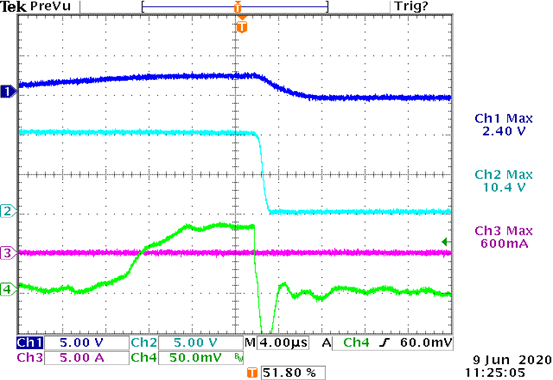

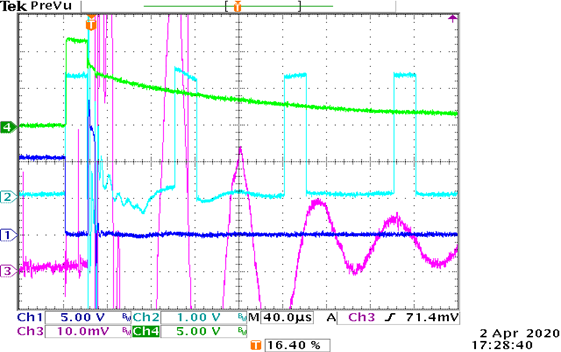

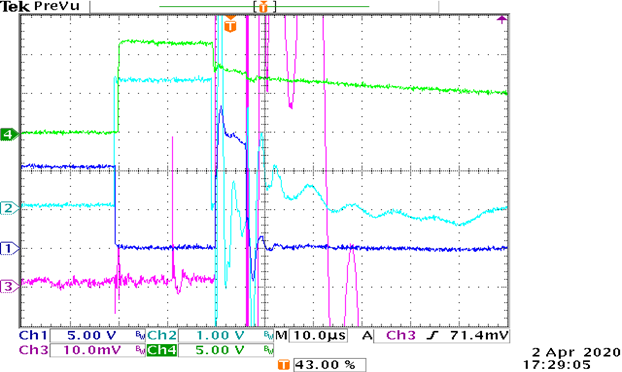

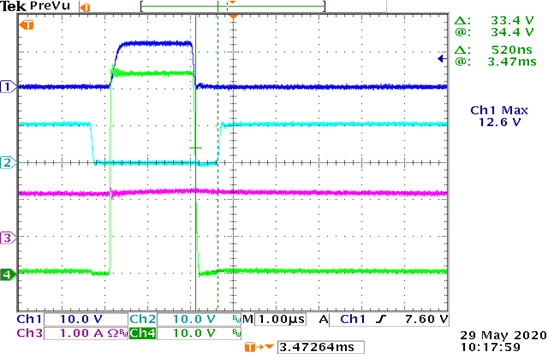

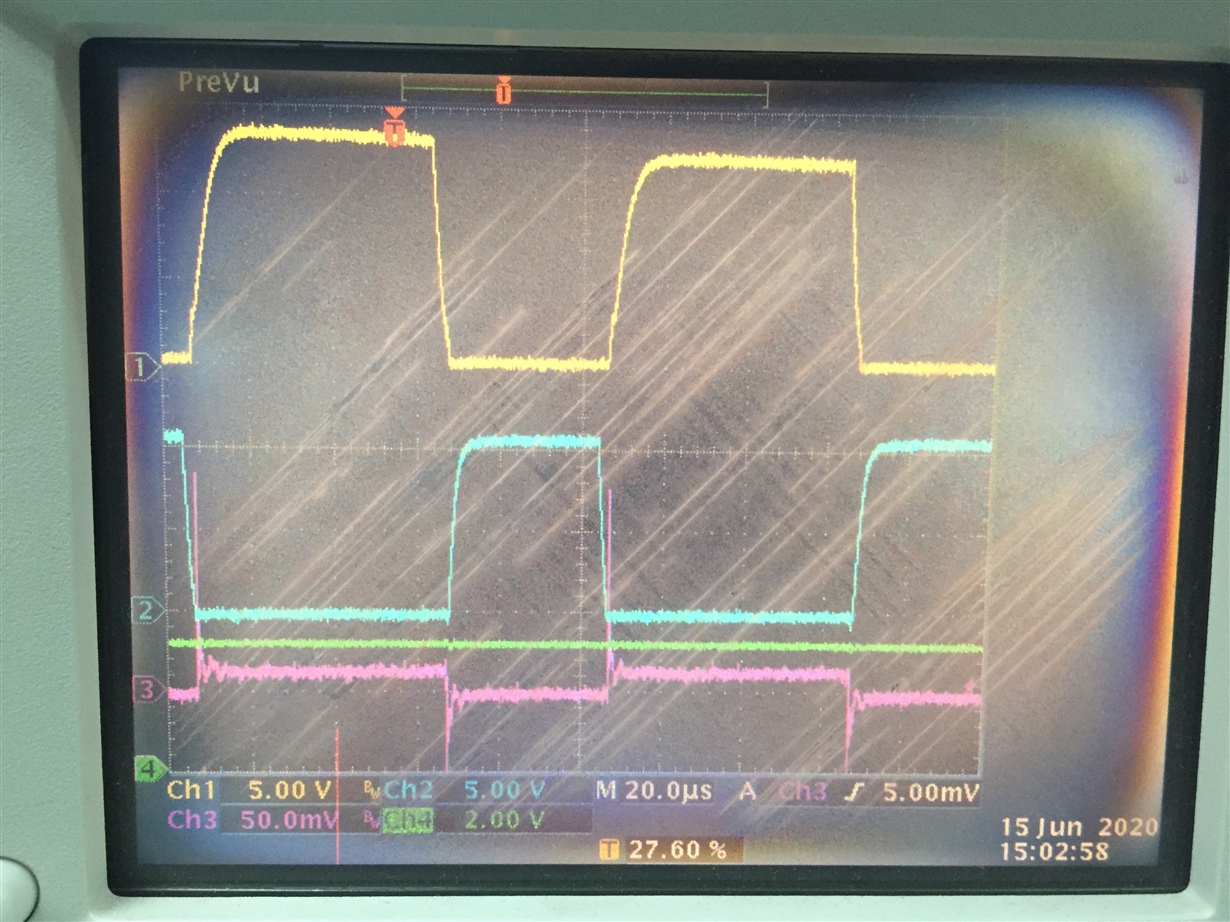

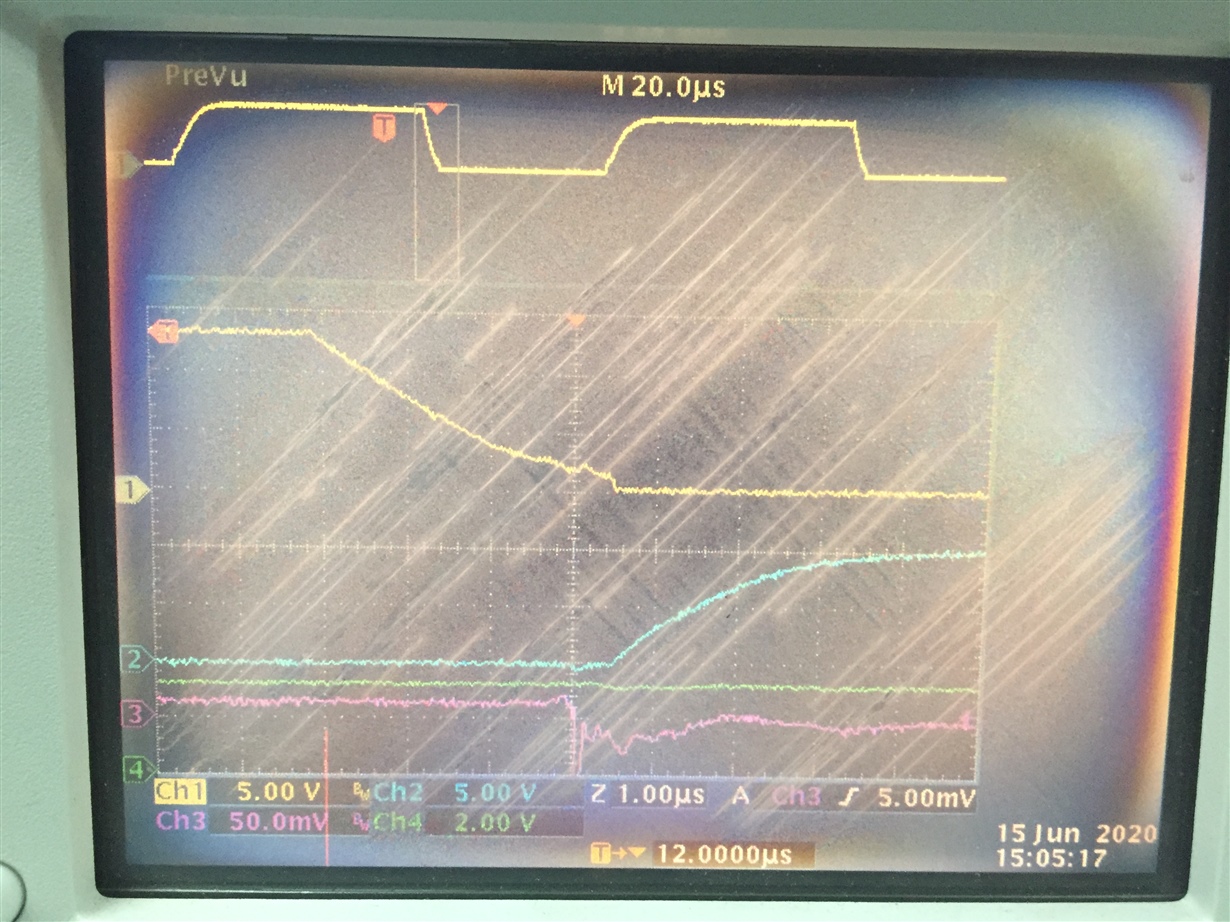

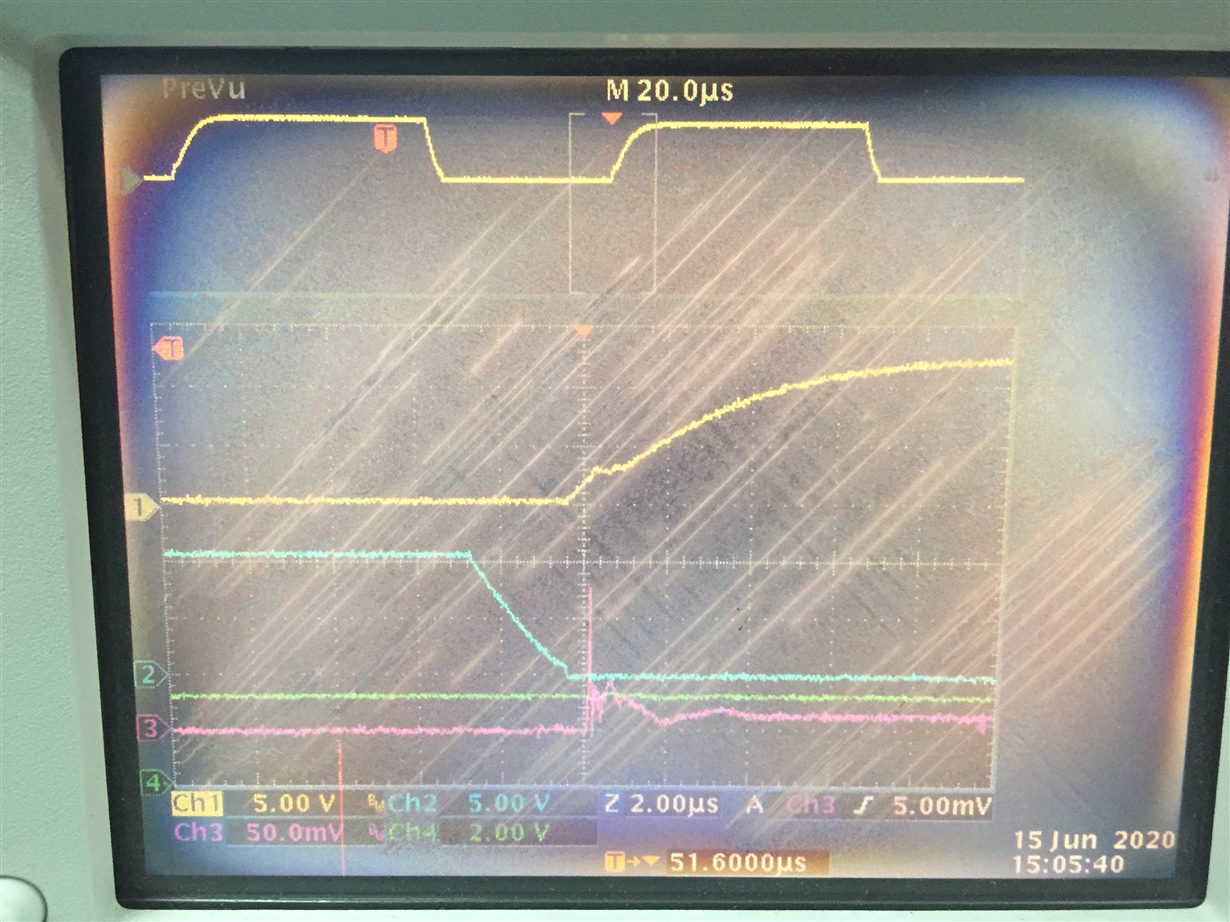

Because I found that when using two phases to control a single coil, the MOS is often damaged,and I caught some abnormal waveforms with an oscilloscope

It can be seen that when the low side MOS is opened, the voltage of high side GS rises, causing a large current

The waveform and my circuit are as follows

| CH1 | The High-Side gate driver of Q15(GS_H with Differential probe) |

| CH2 | The Low-Side gate driver of Q15(GS_L) |

| CH3 | Coil current |

| CH4 | Sampling resistor voltage |

Can you help analyze the reason?

Thanks