Hi,

I'm trying to get a better understanding of the dead time of the driver.

According to data sheet the driver has a digital dead time of ~240ns which starts when the SH pin is in the Hi-Z state (after turning off one mosfet). When does this time start in case of almost 100% pwm, if the low side only switches on for a very short time and SH stays in Hi-Z all the time?

In addition there seems to be another check (FET gate slewing):

"In addition to this digital dead time, the output is Hi-Z as long as the voltage across theGL pin to ground or GH pin to SH pin is less than the FET threshold voltage.

The total dead time is dependent on the IDRIVE resistor setting because a portion of the FET gate ramp (GHand GL pins) includes the observable dead time."

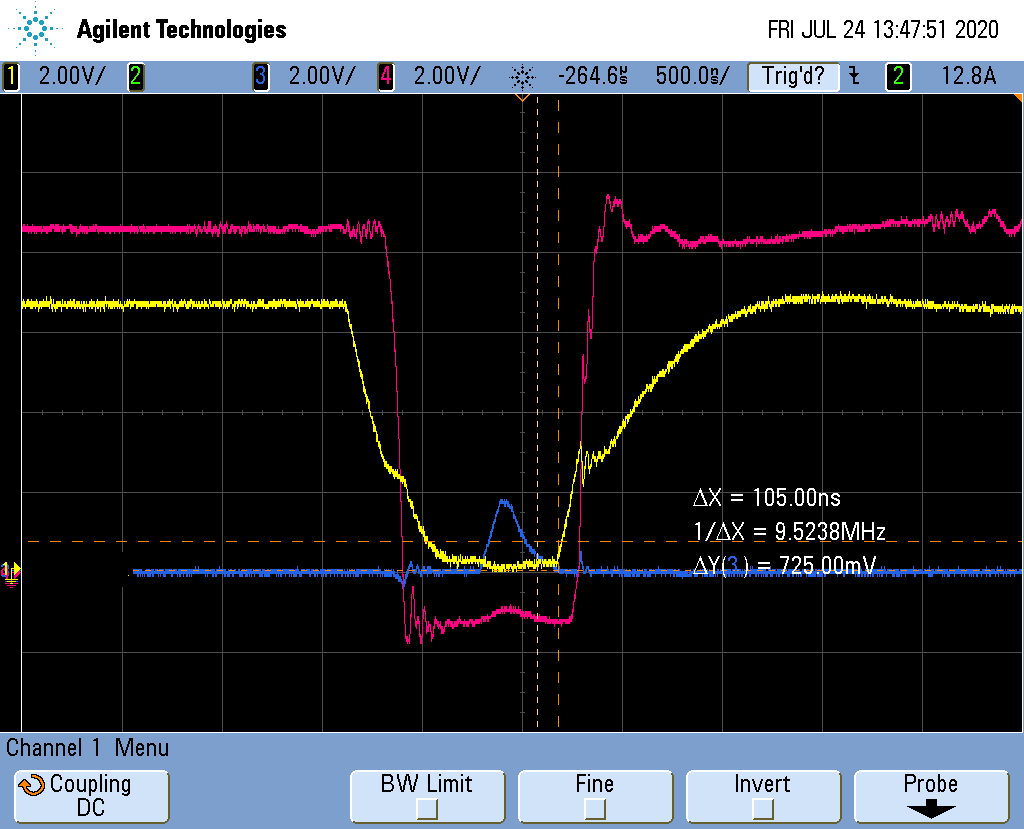

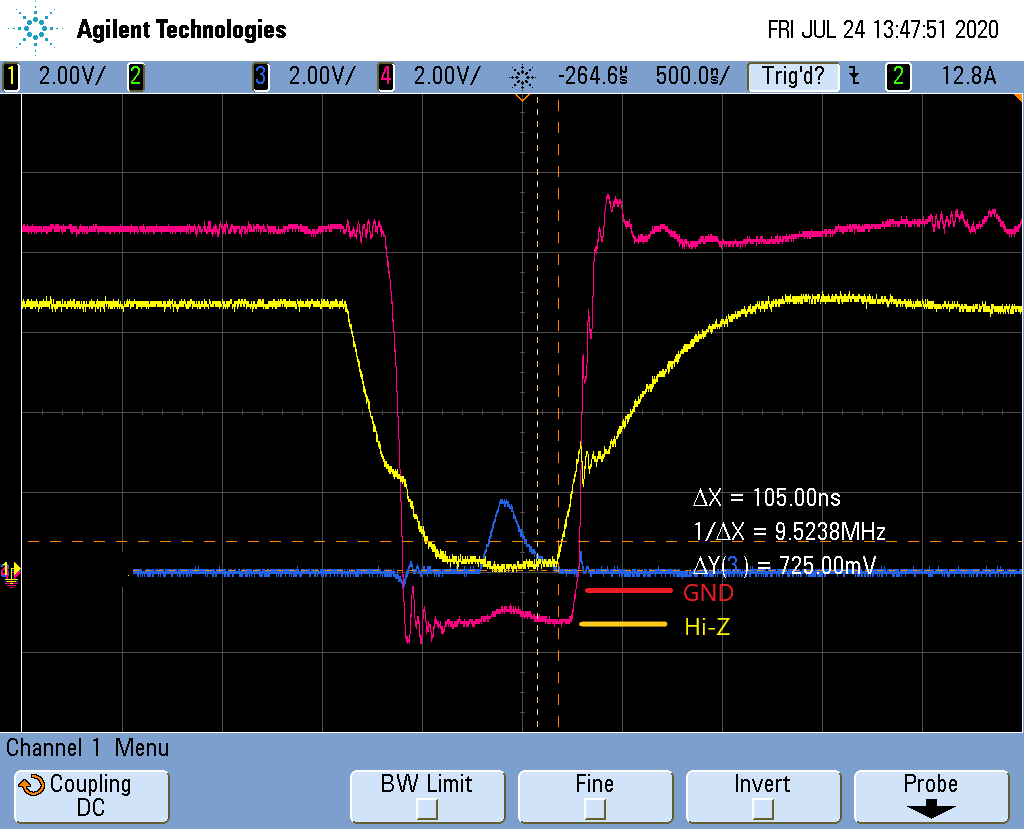

What does it mean "GL to ground"? Because in my measurement below, the strong pulldown of LS and the turn on of the HS starts before GL reach ground.

What does it mean "GH pin to SH pin is less than the FET threshold voltage" ? How does the Driver detect the threshold voltage of the specific mosfet.

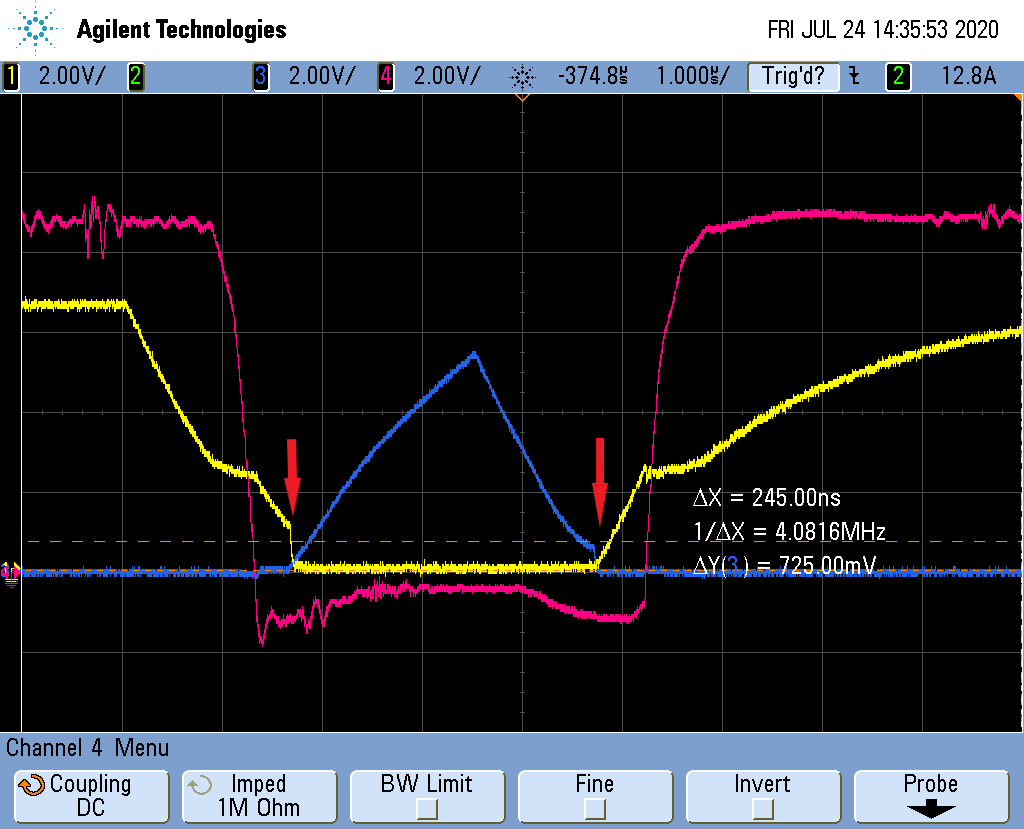

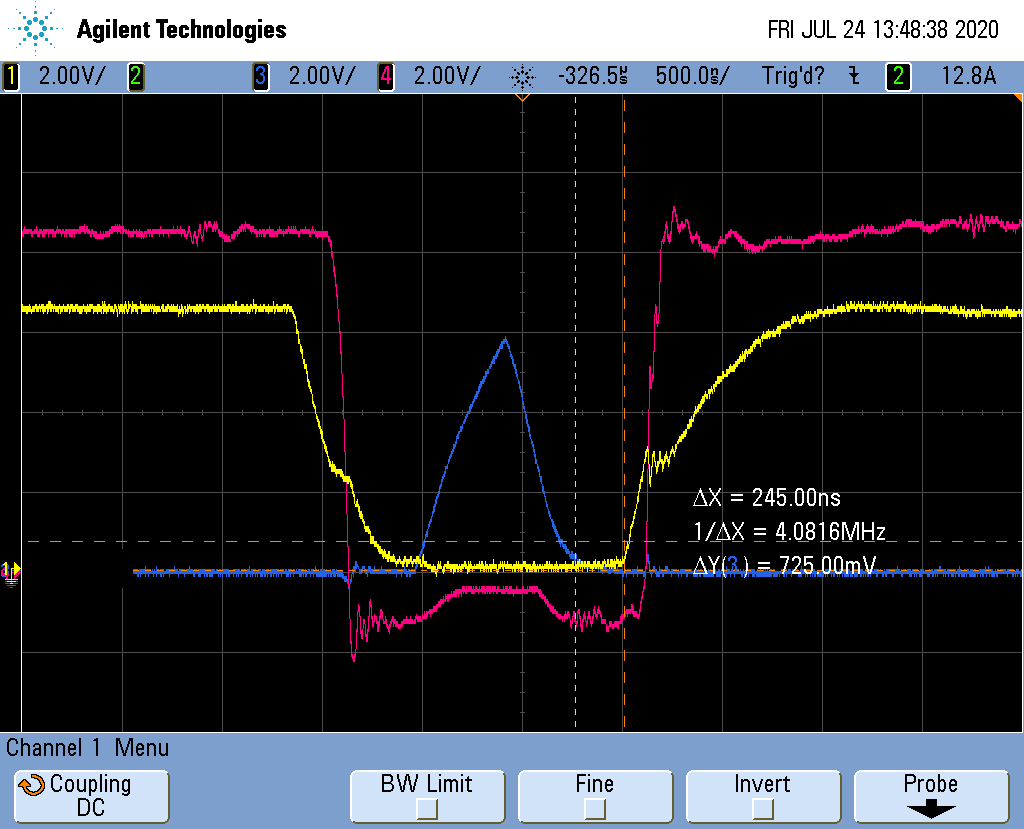

To be able to understand and display this, I have set the switching speed to minimum (IDRIVE on ground):[green=GL; red=GH; blue=SH; yellow= I_Motor]

Best regards

Tobias Schmidt