Other Parts Discussed in Thread: DRV8873,

Hello,

I have several questions regarding FMEA of DRV8873S-Q1 device (SPI version). Could you give me comments on them?

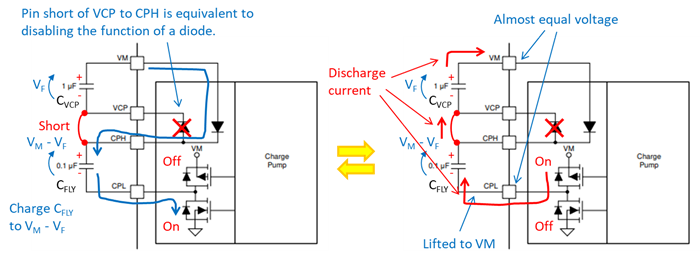

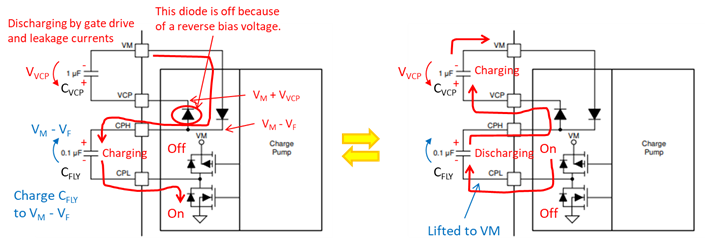

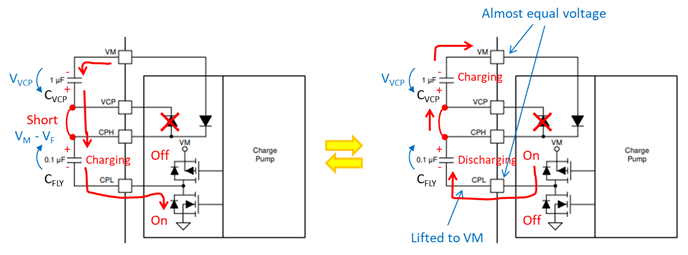

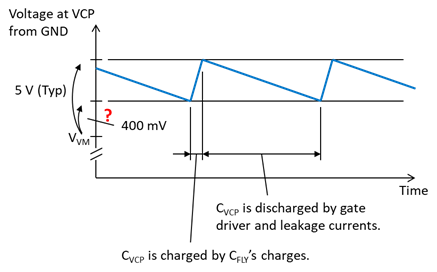

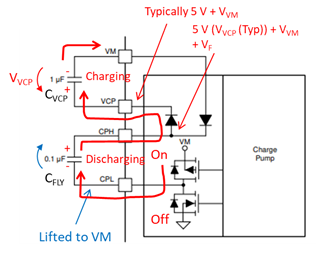

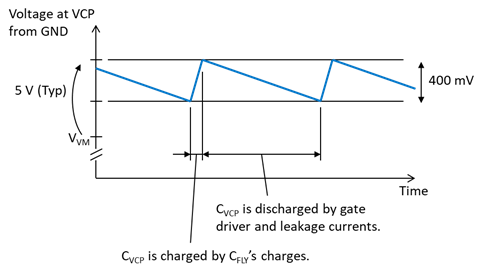

- In order to estimate an impact of the damage of external capacitors (CVCP and/or CFLY), is an equivalent circuit of the charge pump circuit block available?

- What kind of impact can be estimated when a capacitor larger than 1 µF is (accidentally) placed as CDVDD at DVDD pin?

- What kind of impact can be estimated when the capacitance of CVCP (at VCP pin to VM) increases by double or reduces by half?

- What kind of impact can be estimated when the capacitance of CFLY (between CPH and CPL pins) increases by double or reduces by half?

- The apps note "DRV8873-Q1 Functional Safety FIT Rate, FMD and Pin FMA" (SLVAEV2) says in Table 10, "Device will not power up" when a VM pin is open.

- However, there are two VM pins in a DRV8873S-Q1, I guess it can power up when only one VM pin is open and the other VM pin is supplied. Could you review it again?

- What kind of impact can be estimated when DVDD pin is accidentally short-circuited to a different 5 V in the same circuit?

- Under the conditions - VM is on, and VM is off.

Best regards,

Shinichi Yokota