Hi team,

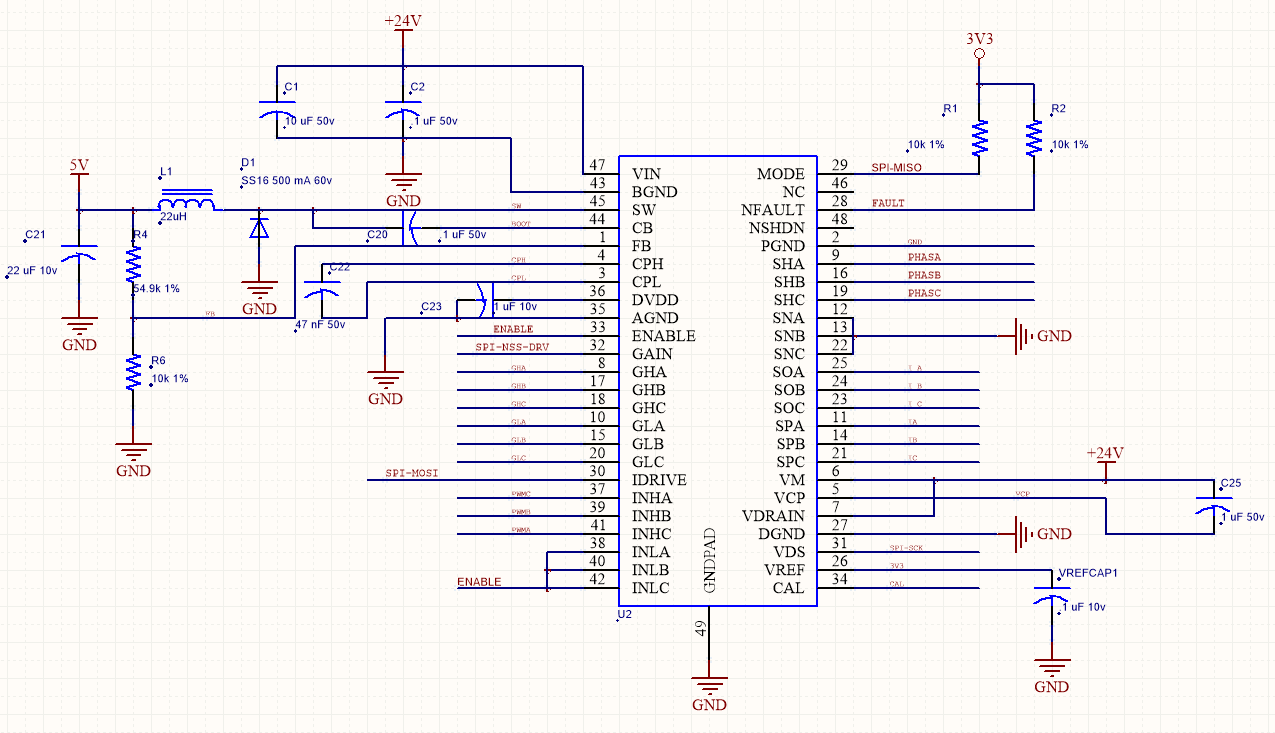

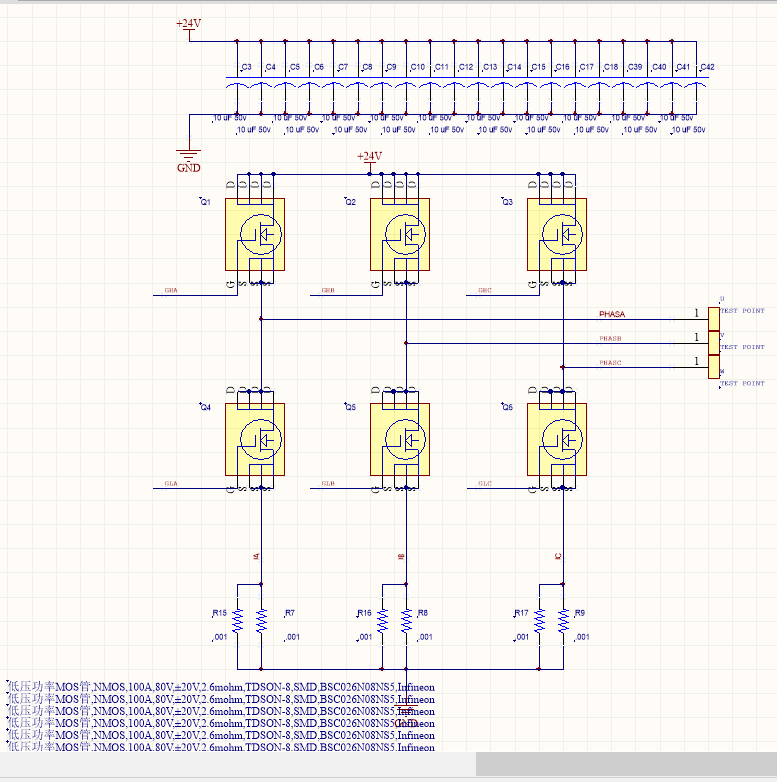

My customer is using DRV8323RH for 24V 50A application scenario. they found severe thermal issue.

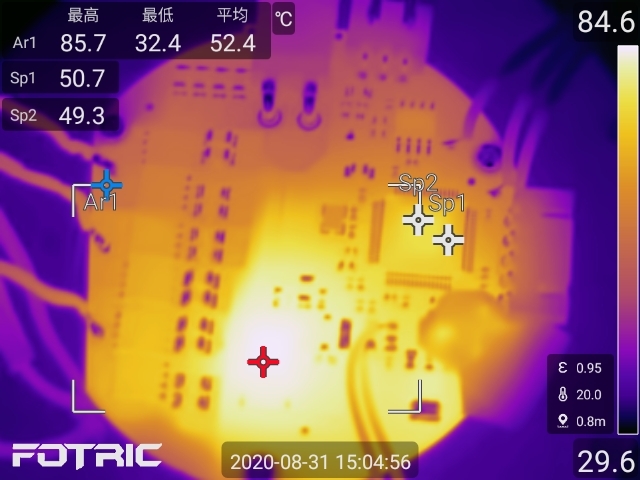

1. Motor with no load running, the temp can be up to 85℃;

2. Even using external power supply (not buck in the schematic), the temp is still very high;

3. Changing MOSFET from BSC026N08NS5(80V 100A) to TPH2R506PL(60V 100A) with lower Cds,the temp is reduced to 75℃, but still very high;

So, we doubt that whether it's due to Cds of MOSFET. However, even using MOSFET with lower Cds, the temp is still very high.

Questions:

1. Do you meet this thermal issue in other customers?

2. Do you have some suggestions to reduce the temp? I propose to add heat sink. But customer feed back that it will increase cost.

3. Do you have better IC for recommandation?

thanks a lot.

Best regards,

Yang