Hello TI Support,

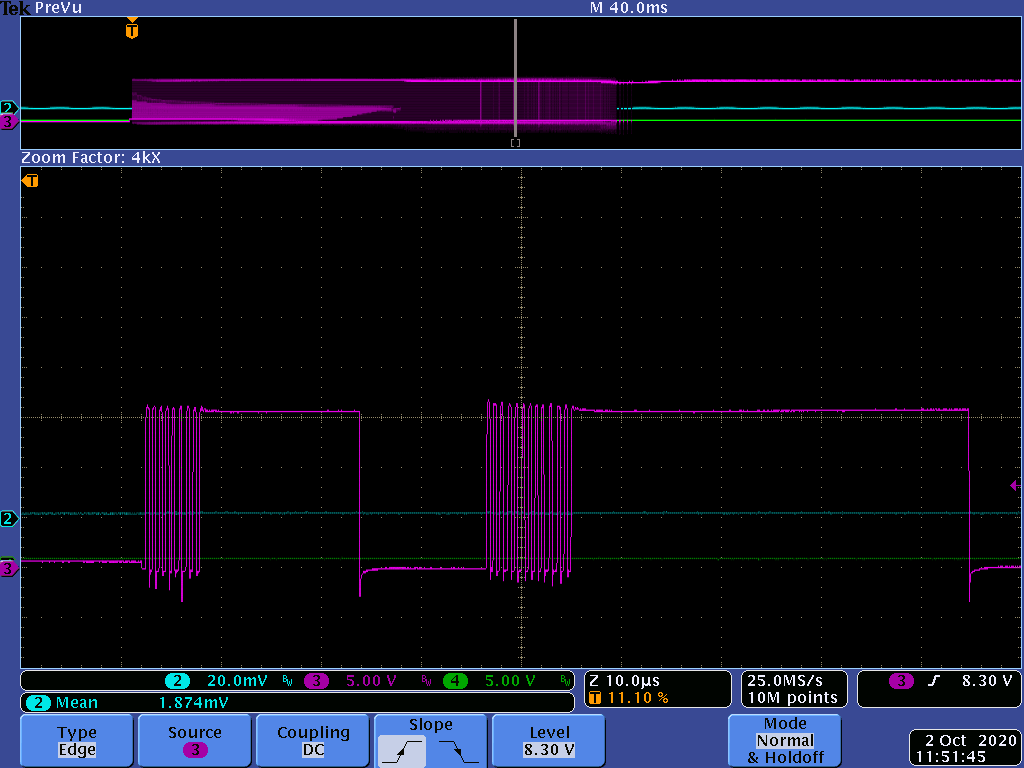

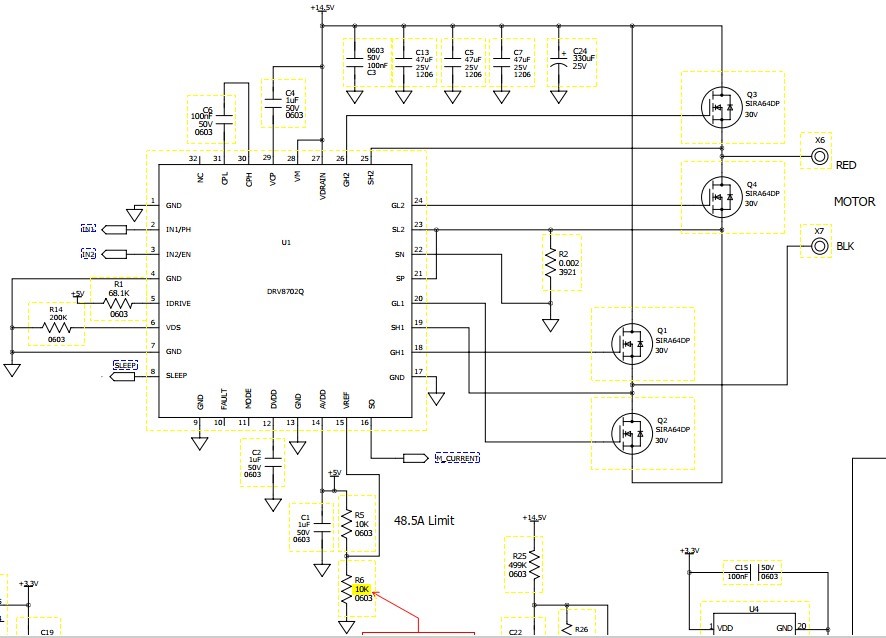

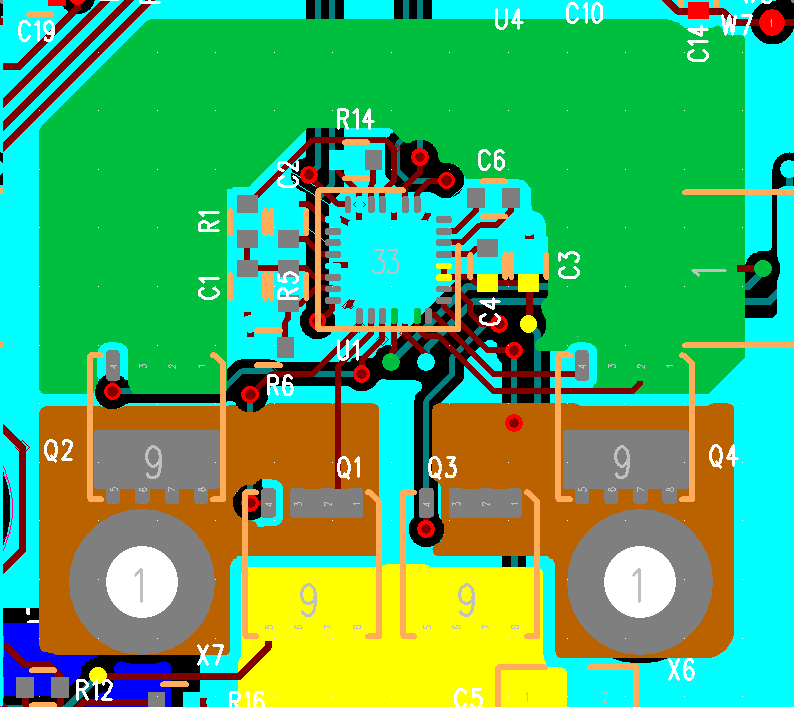

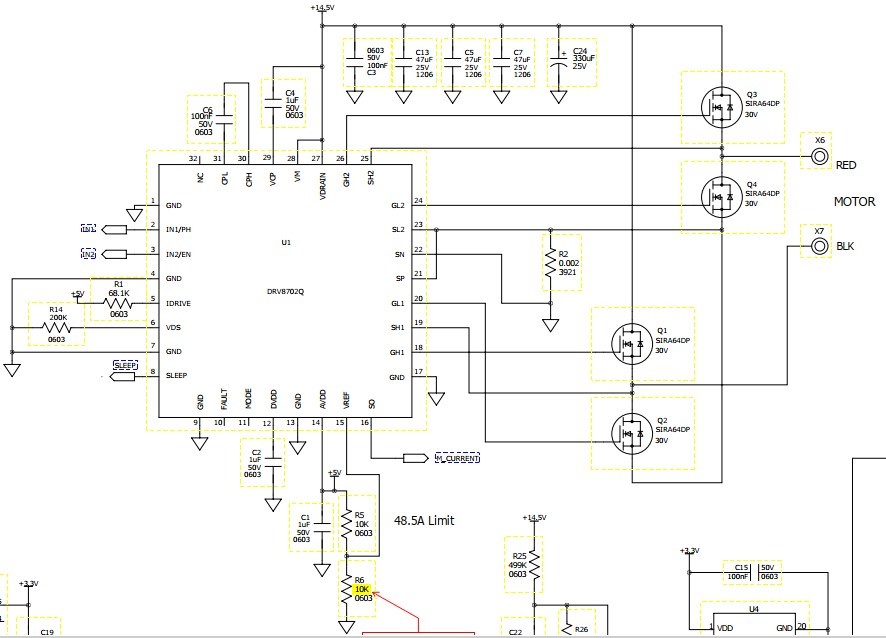

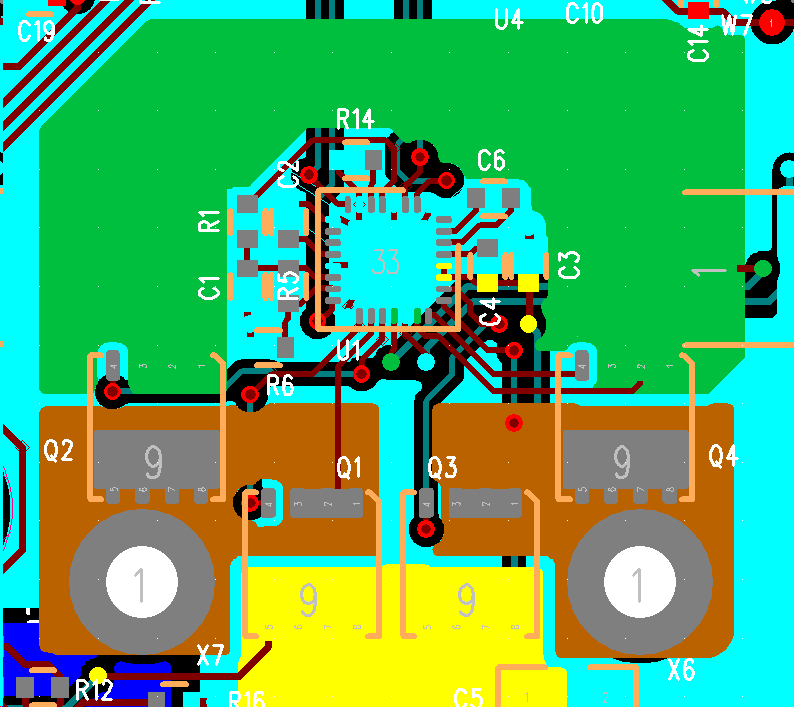

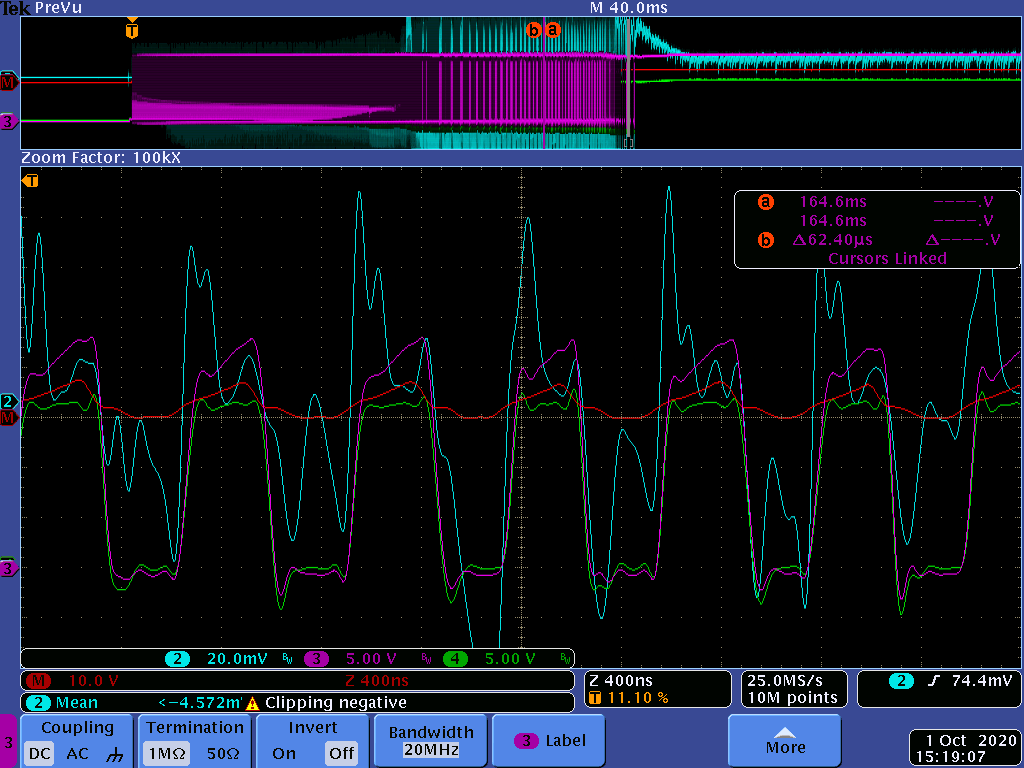

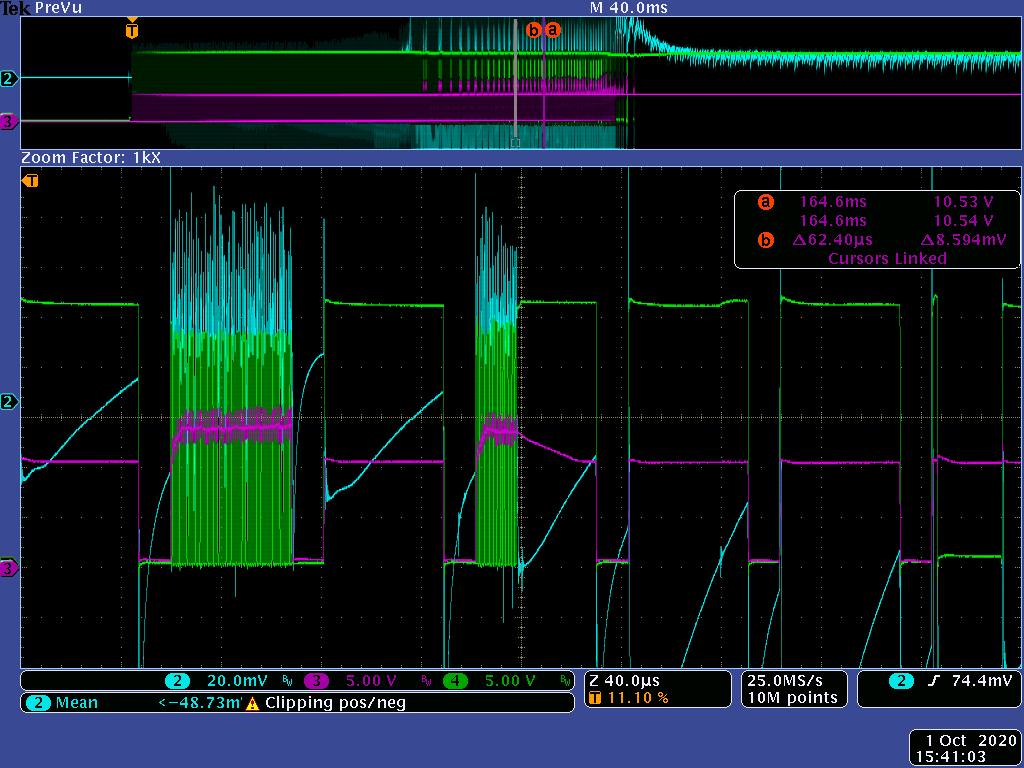

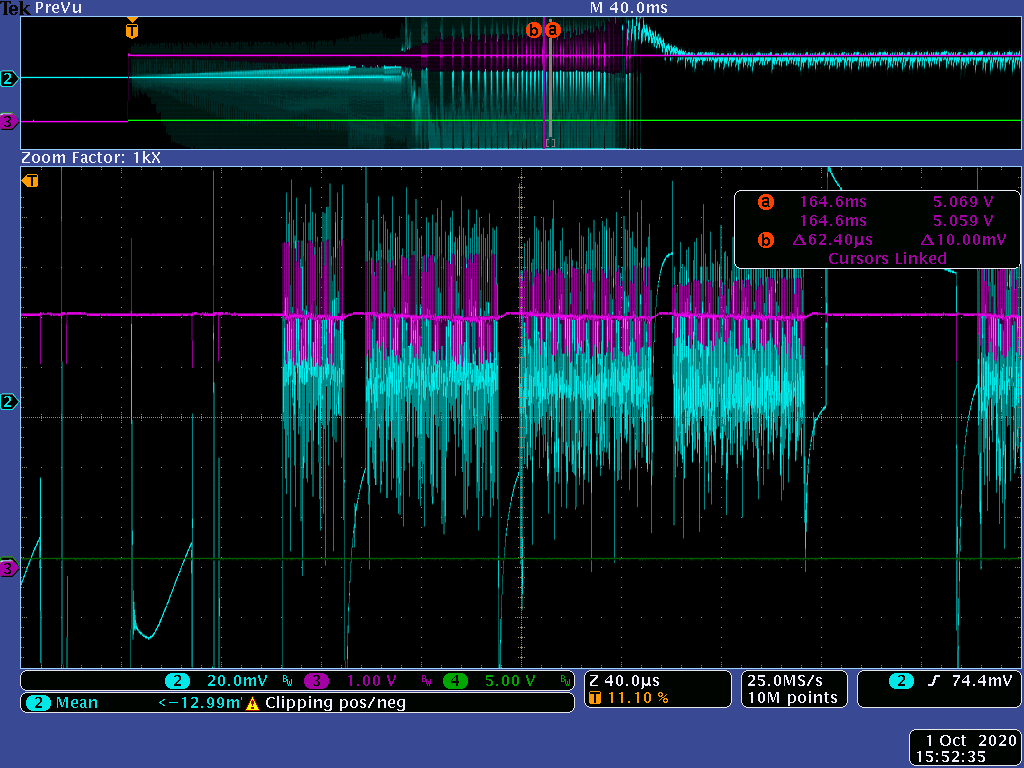

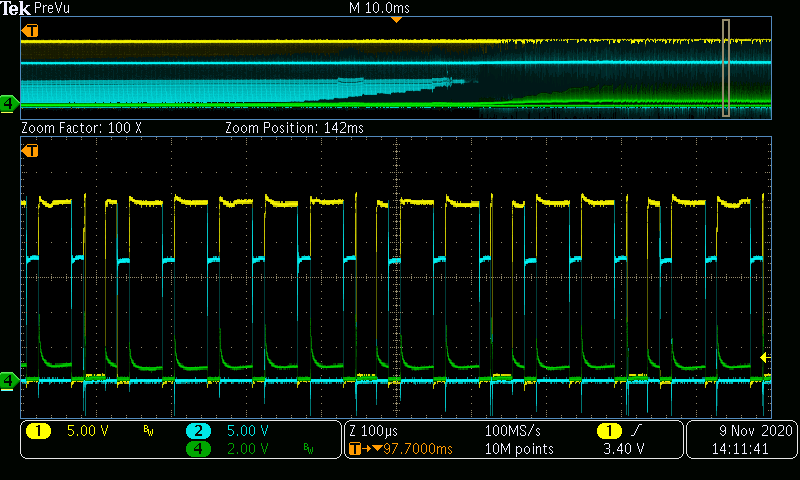

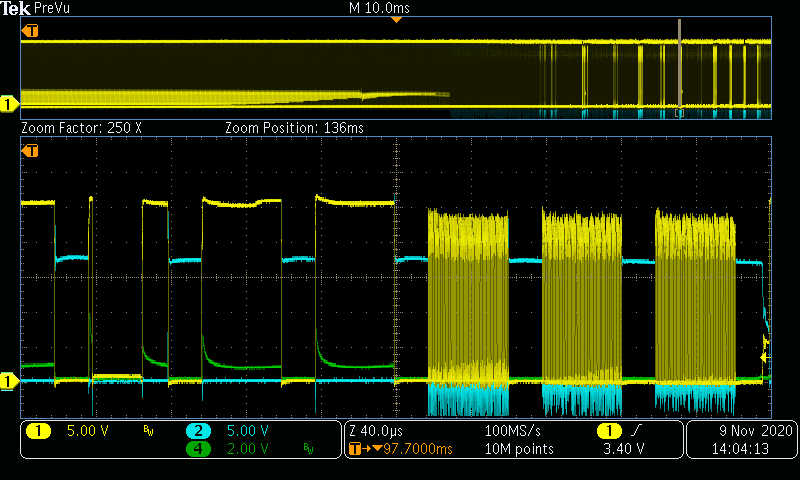

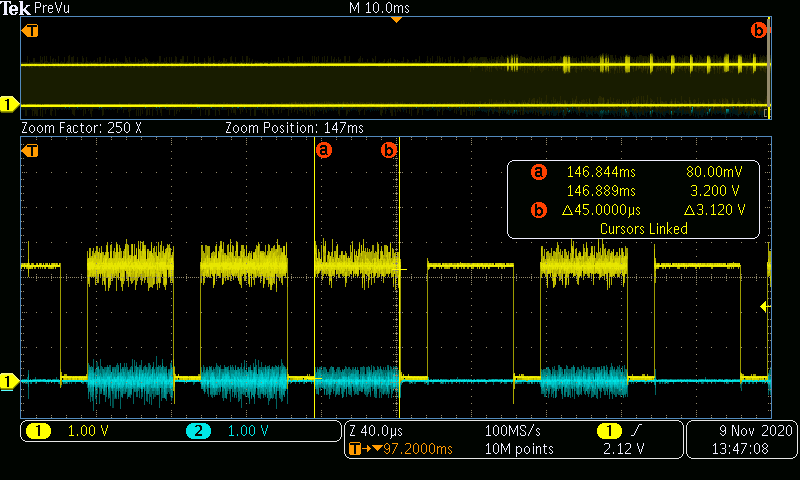

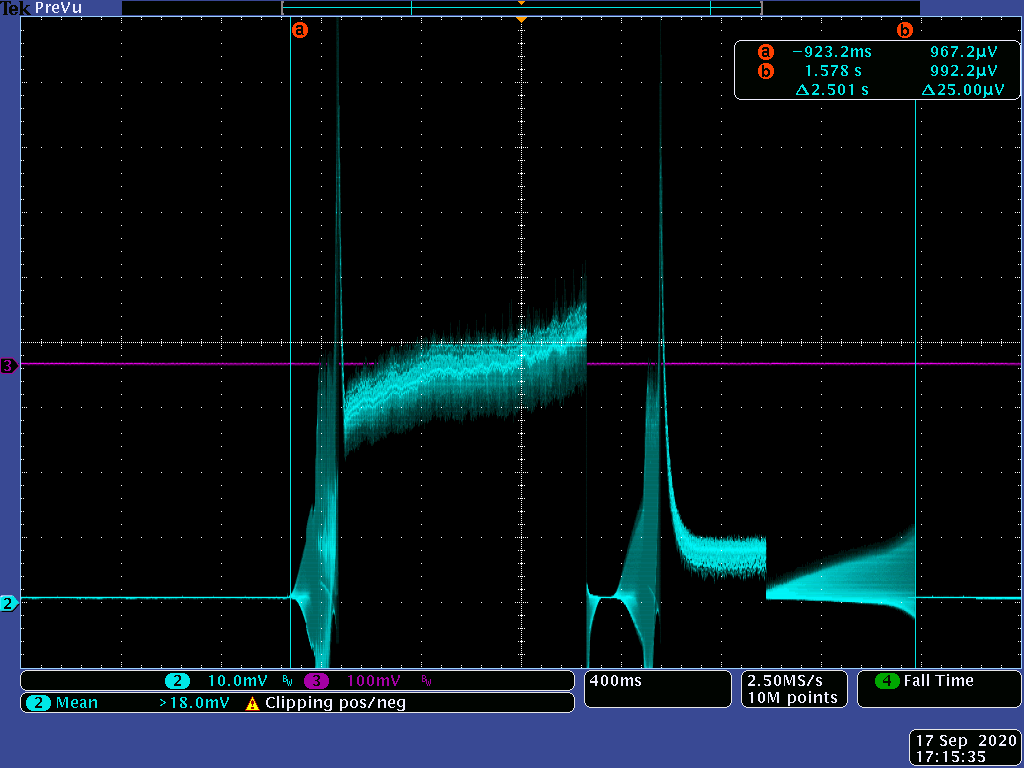

Hopefully the schematic and layout portions of the DRV8702 pasted okay above. I'm having an issue with the DRV8702 in that the high side gate driver starts to pulse VERY fast. The attached screenshot of the source pin of Q1 shows that it is being turned on and off at a 50% duty cycle with a period of 300nS. That doesn't match up any fault conditions that I can find in the datasheet, so I believe the DRV8702 is malfunctioning. I'm not able to check the nFAULT pin, as it is not used in this design. I've replaced the part, and played with decoupling capacitors and grounding but am unable to get the part to consistently drive the FETs. When Q1 is being driven this way, Q3 remains on. If this high frequency glitch occurs for too long, Q1 fails short (this was how I found this phenomena).

Do you have any recommendations on what to look for to try to fix this issue? The application is a drill motor driver. These gate pulse issue only occur during the soft start portion of the motor while we PWM the IN1 and IN2 pins. You can see in the above scope shot that once the DRV8702 reached 100% duty cycle that things behave normally. The gate pulses do not happen all the time, but when they do it is always on the rising edge of the source pin.

Let me know if you've ever seen this before and what you recommend to do to try and fix this!