Other Parts Discussed in Thread: DRV8305

Hi

My customer is using DRV8305-Q1EVM for testing.

it doesn't used DSP and DSP interface Deleted in the EVM.

The configuration register of DRV8305EVM is using default setting , only used the 6-PWM Mode configuration.

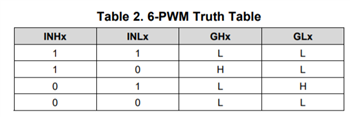

In the datasheet of DRV8305, When both INHx and INLx are set low, GHx is expected Low.

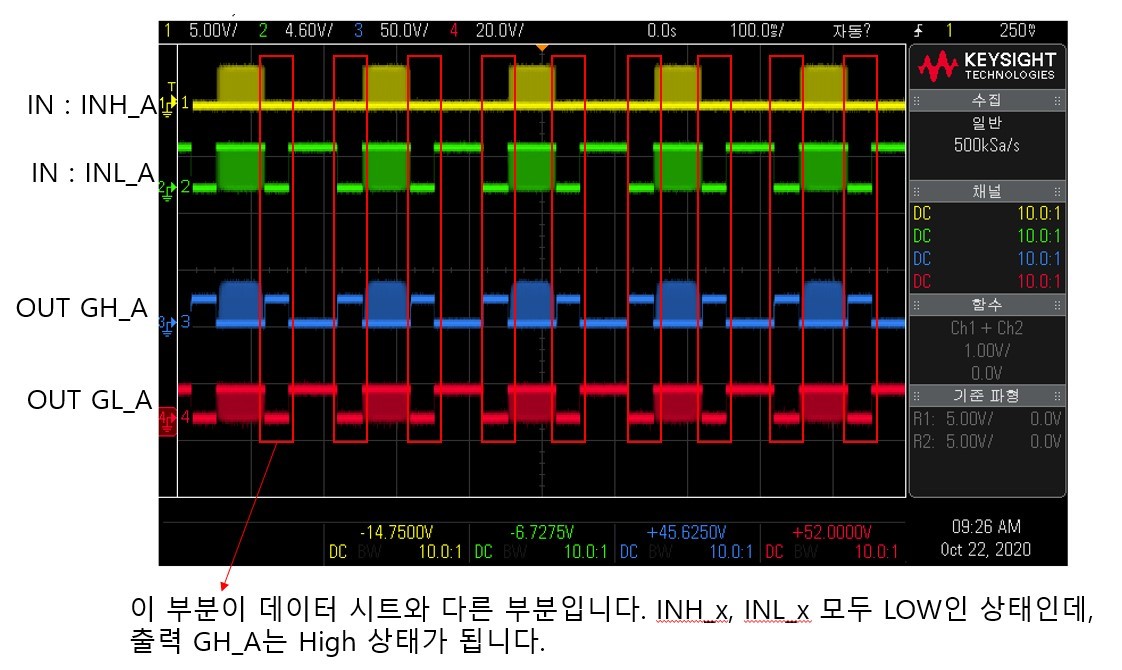

but When both INHx and INLx are set low, GHx was High as below attached waveform.

He want to turn off both high-side FET and Low-side FET.

pleas check and reply.

thanks.