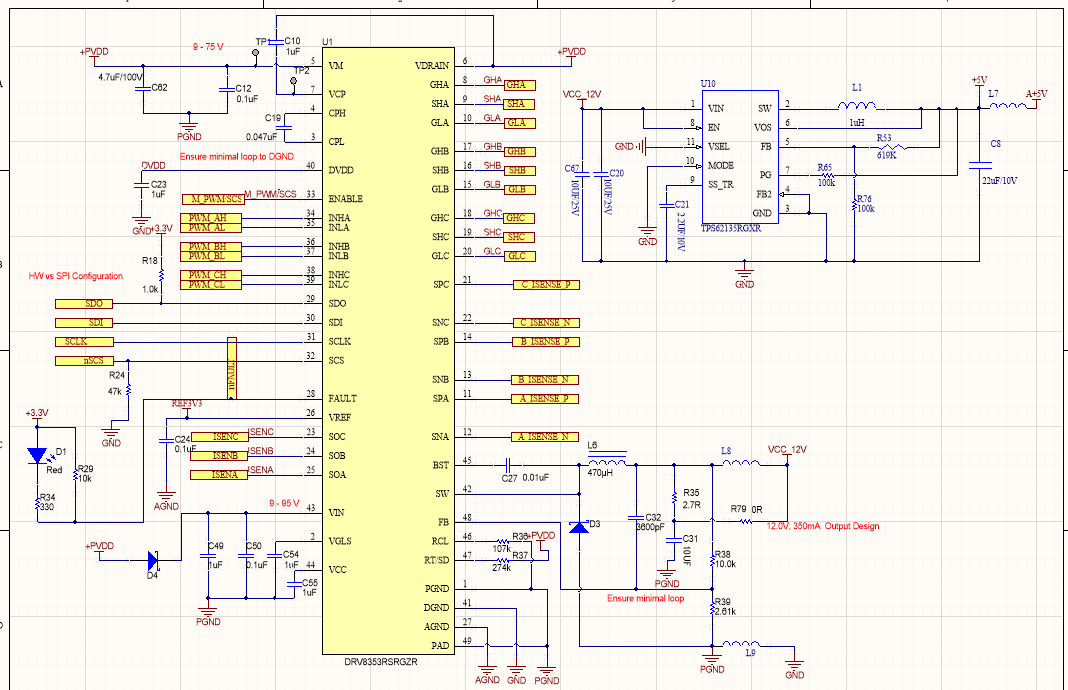

Other Parts Discussed in Thread: DRV8353

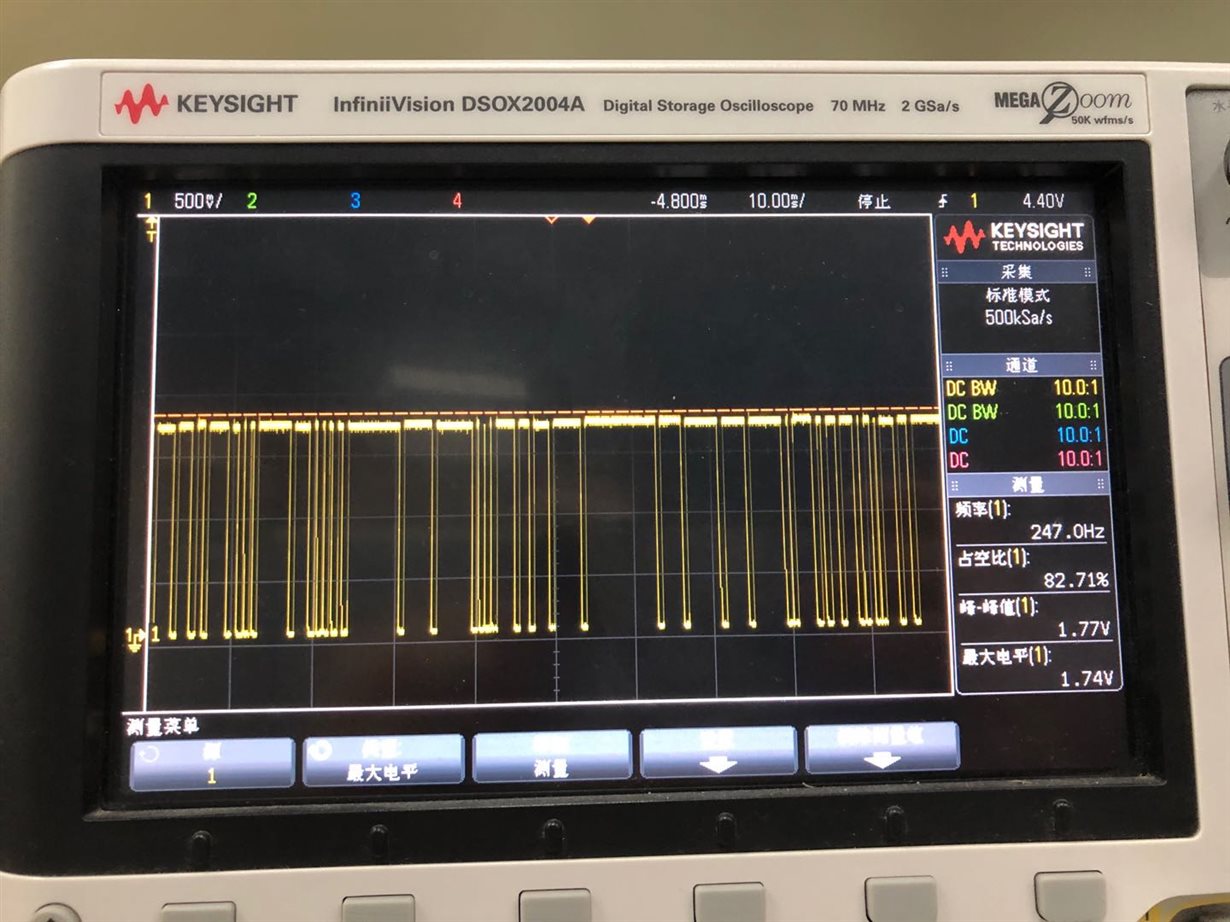

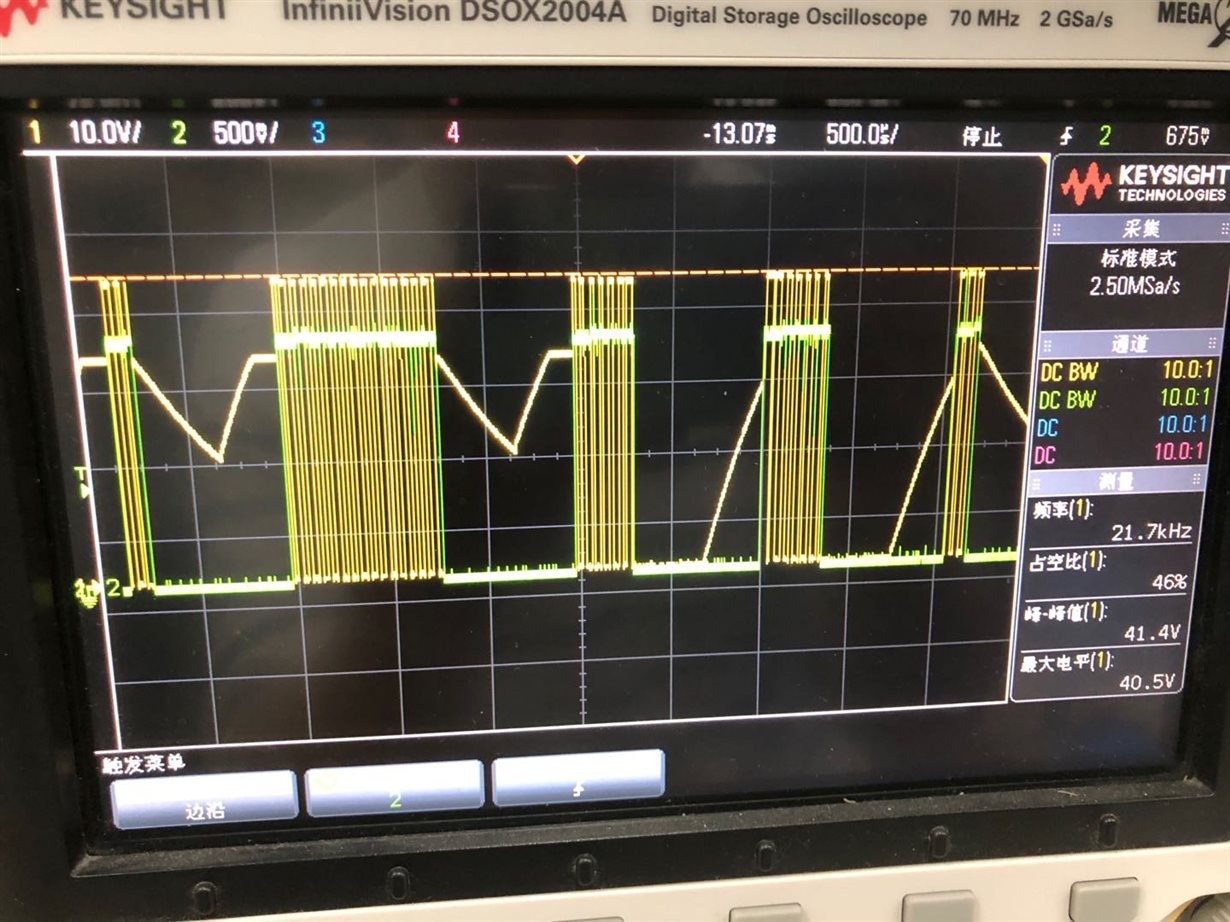

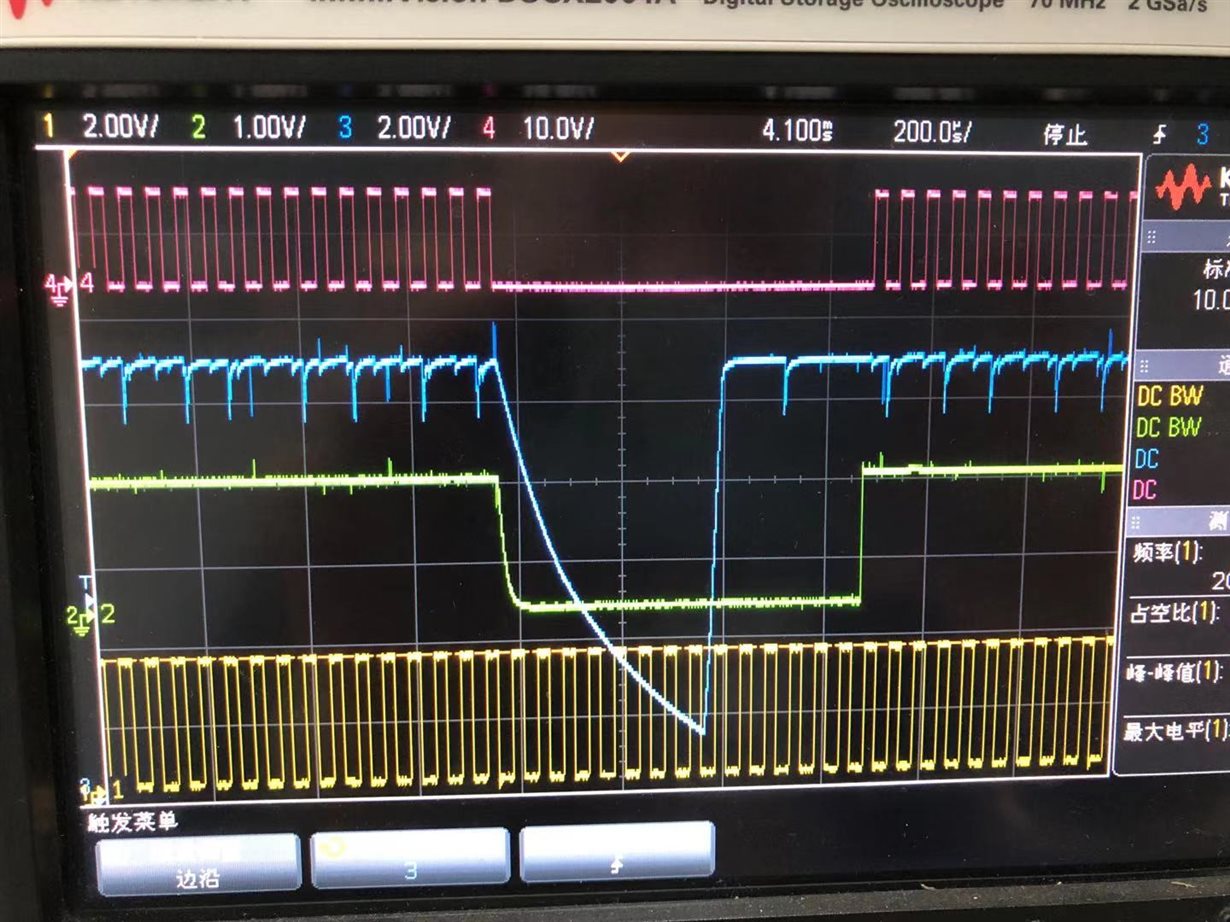

We are using DRV8353 to drive BLDC motors. At present, it is found that the output waveform of the SOC \ SOB \ SOA pin when the BLDC motor is not connected is shown in the figure. The waveform should be 1.65V. It is abnormal at present, similar to PWM wave and cannot be used. May I ask what causes this phenomenon.