Other Parts Discussed in Thread: DRV8332, DRV8312, DRV8353

Hi

In our boards evaluation, following phenomenon is occurred.

I would like to ask about gate drive of DRV8353HR.

(Phenomenon)

- If I use PWM frequency 200kHz, less than duty 5%(lass than high time 250ns) , this driver's gate control was not operated.

-Even if a fixed Duty PWM signal is input to INHx. Gate Drive on duty seems to slightly change automatically.

( It is using 3×PWM mode. Since we are doing first evaluation, I am useing with INHA:High, INHB & INHC:Low. I haven't controlled the motor yet.)

(Question)

- Are there any requirement of minimum on duty cycle of PWM?

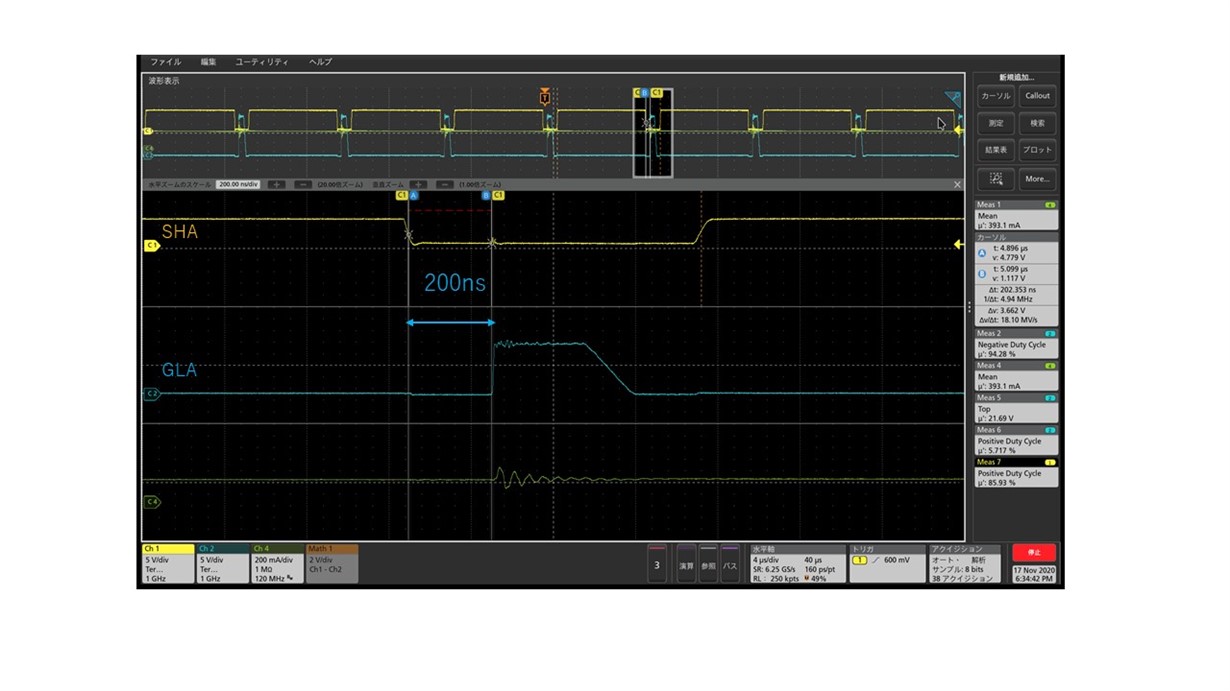

- I checked GLA and SHA signal, it seems deadtime is 200ns,(Attached file )

According to the datasheet, gate drive dead time is 100ns(HW device).

Is this time changed automatically?

- Even if a fixed Duty PWM signal is input to INHx(3×PWM mode). Is gate frive on duty cycle slightly change automatically?

In short, isn't the current value fixed even with a fixed-duty PWM signal input?

Best regards

Naoki