Hello,

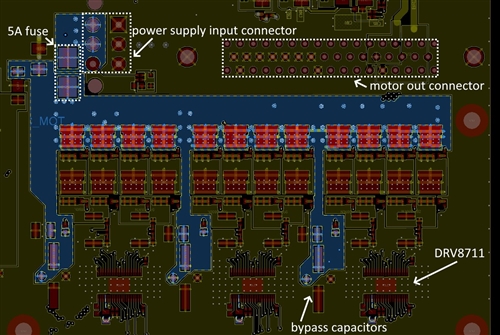

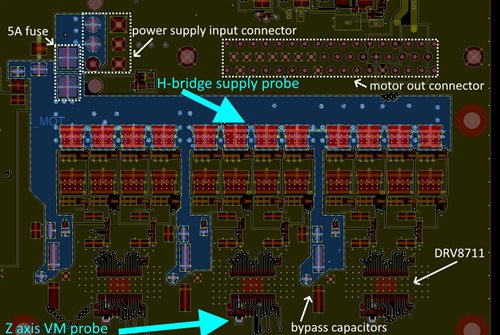

Some of our boards using the DRV8711 trigs OCP errors (50/2000 boards).

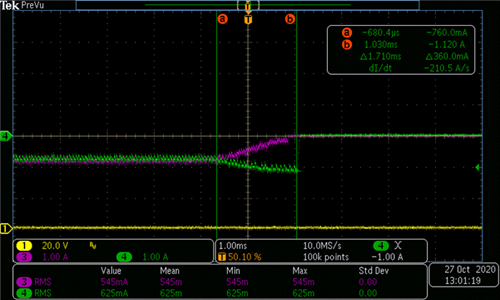

These boards operate normally few months, then errors happens every time at the same motor position (ie: when A phase become positive)

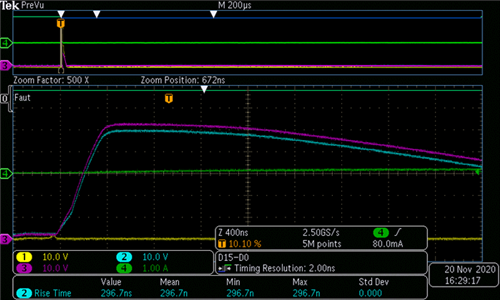

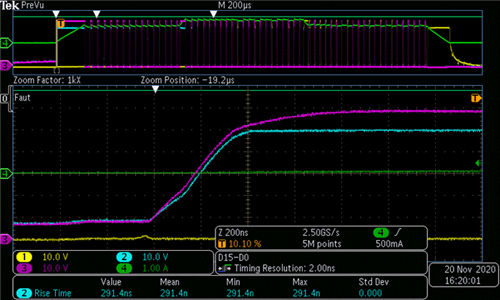

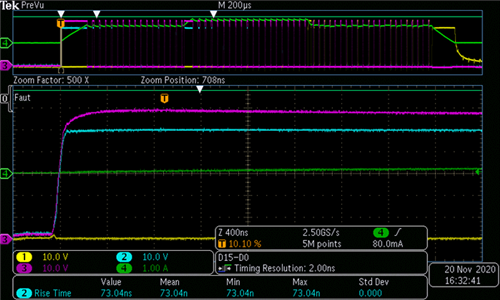

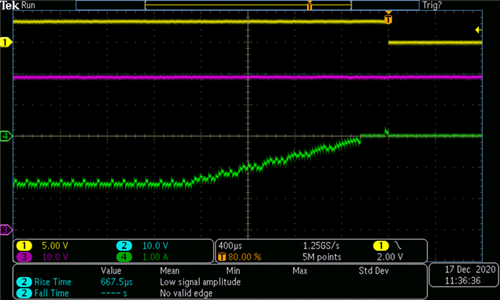

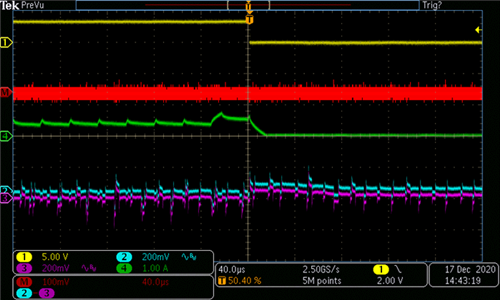

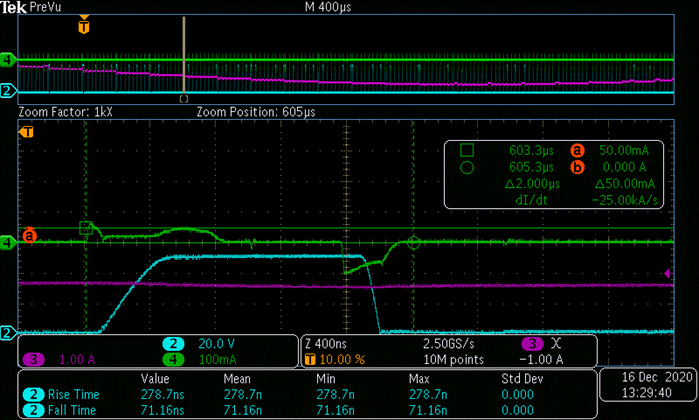

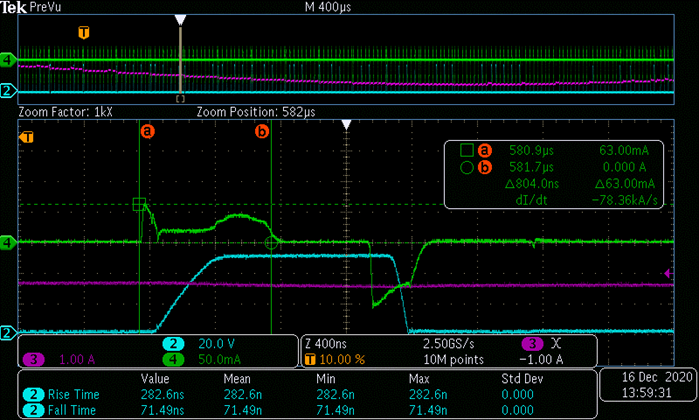

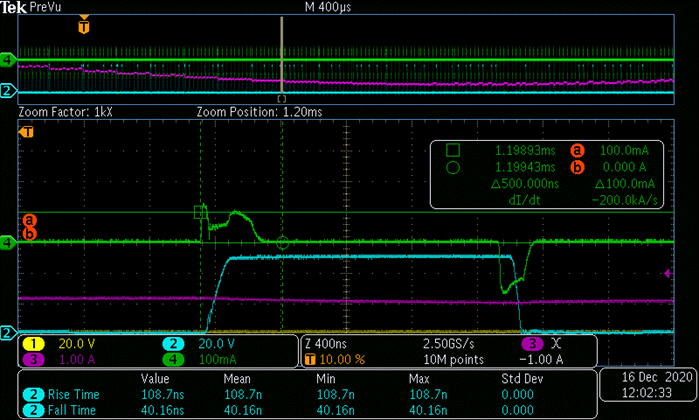

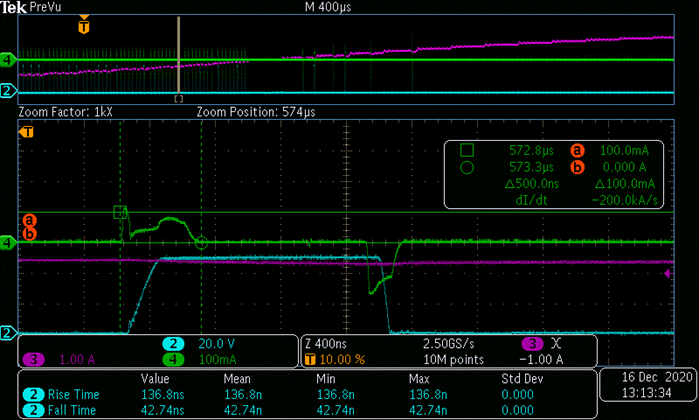

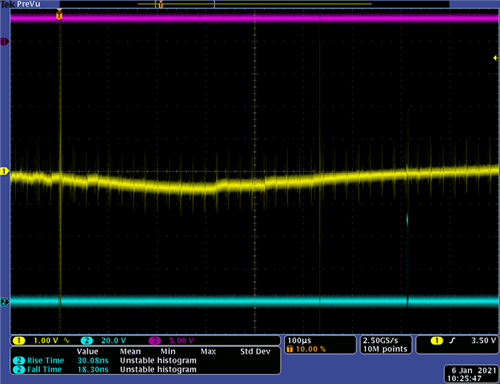

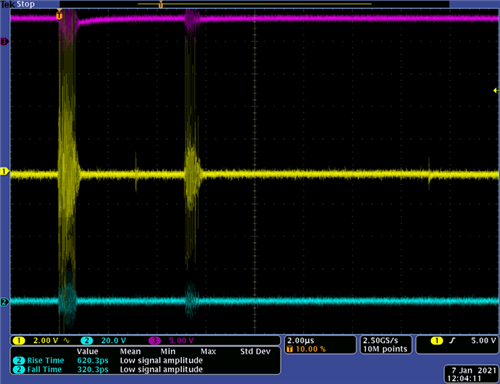

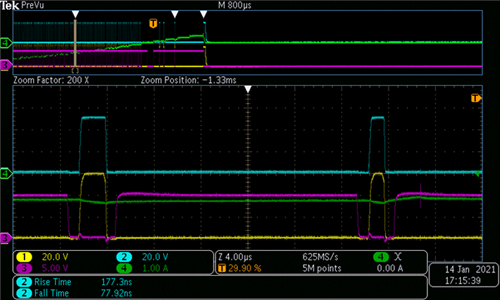

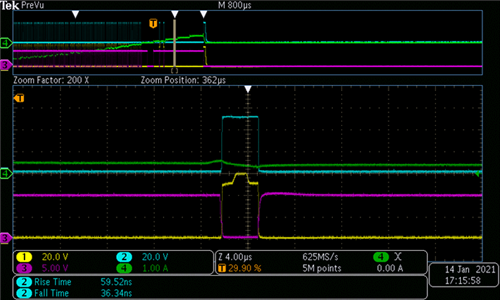

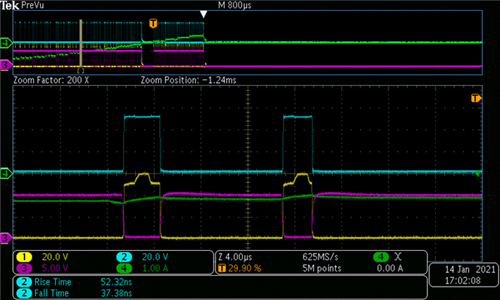

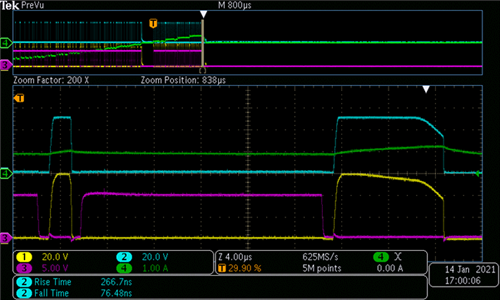

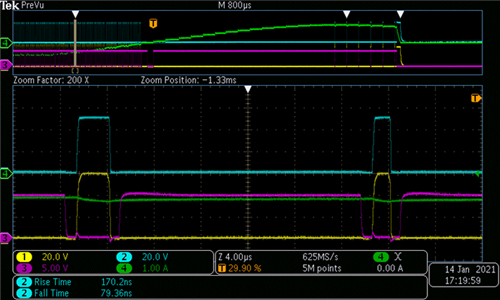

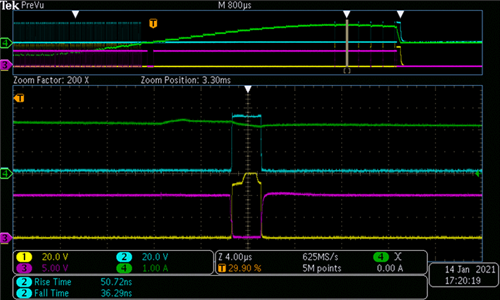

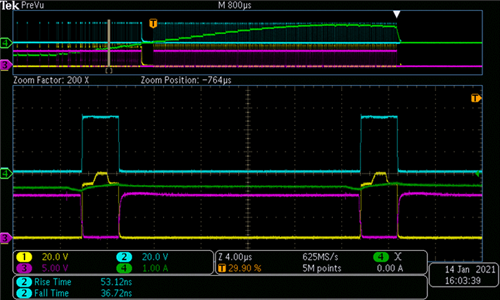

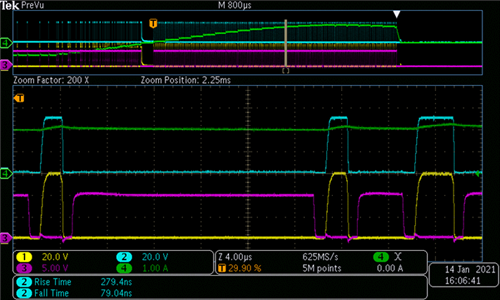

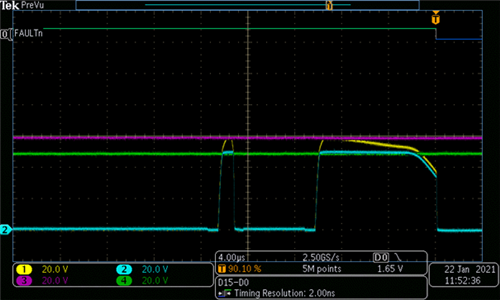

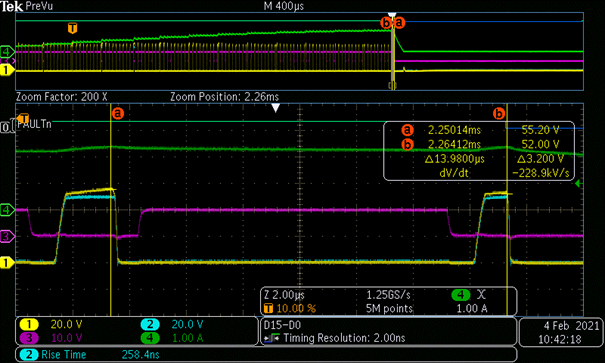

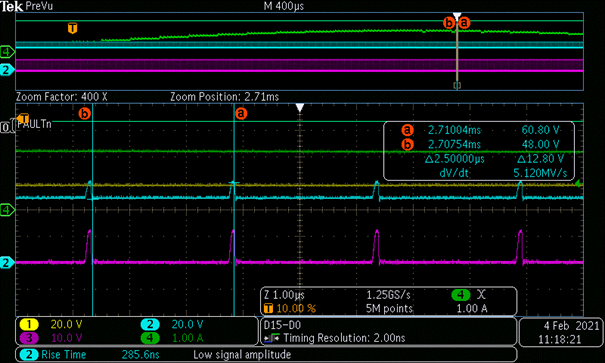

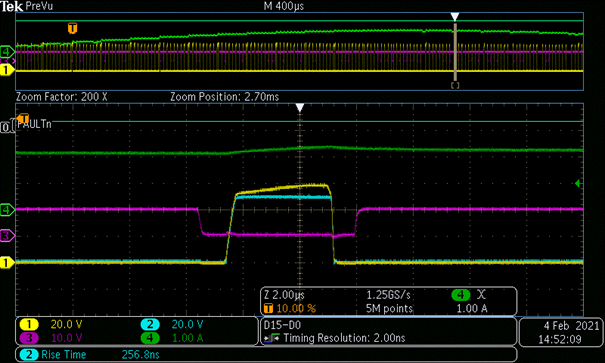

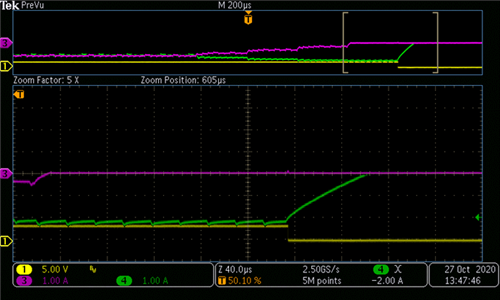

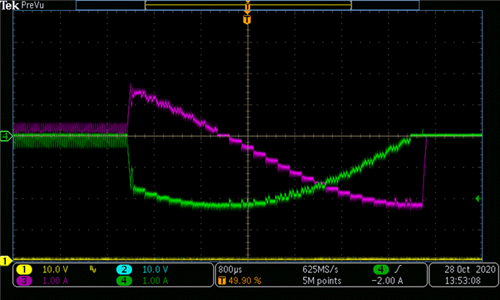

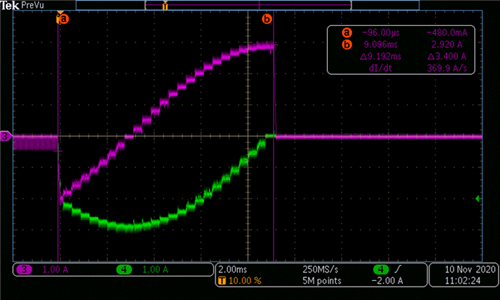

For each boards concerned by this issue, we measure abnormally long rise time at the output of one high side MOSFET (more than 300ns when all other are less than 180ns).

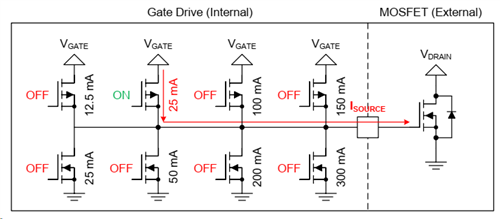

Below our standard DRIVE register parameters:

00 --OCP OCP threshold

00 --OCPDEG OCP deglitch time

01 --TDRIVEN Low-side gate drive time

01 --TDRIVEP High-side gate drive time

00 --IDRIVEN Low-side gate drive peak current

00 --IDRIVEP High-side gate drive peak current

Using these new parameters improve but the issue still exist:

01 --OCPDEG OCP deglitch time

11 --TDRIVEN Low-side gate drive time

11 --TDRIVEP High-side gate drive time

No change when we replace the MOSFET.

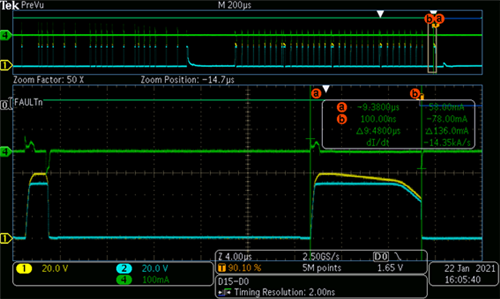

But rise time is then fine after replacing the DRV8711 by a brand new.

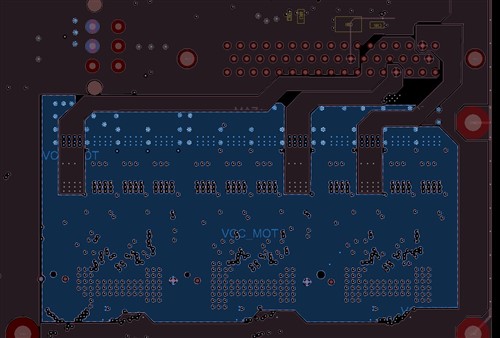

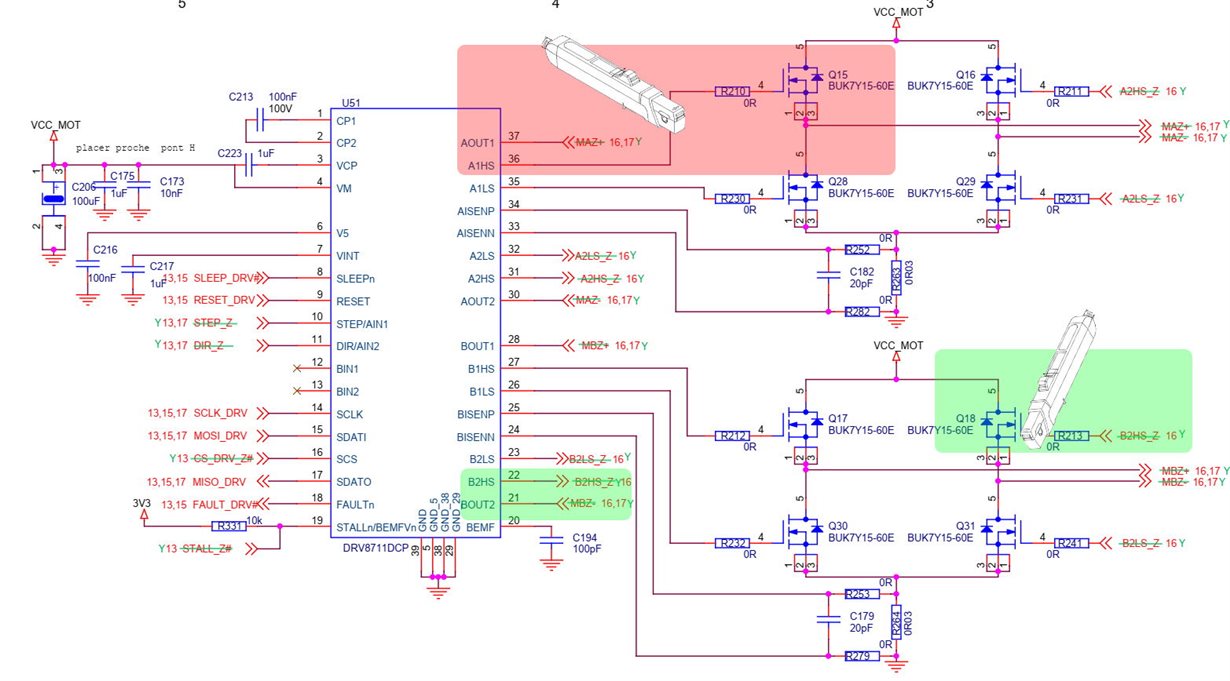

See attached schematic CN6-22D_SCH_DRVX+Z.pdf

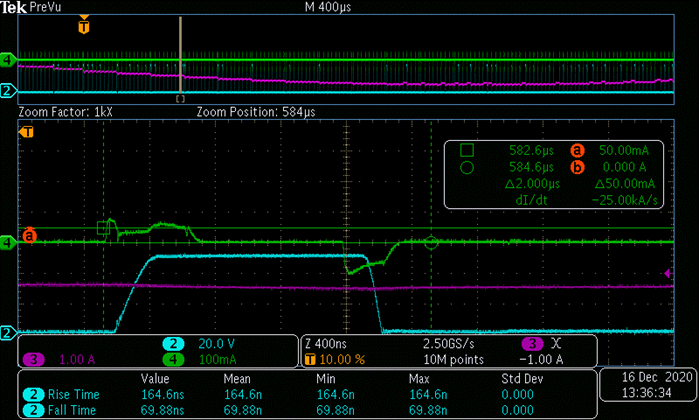

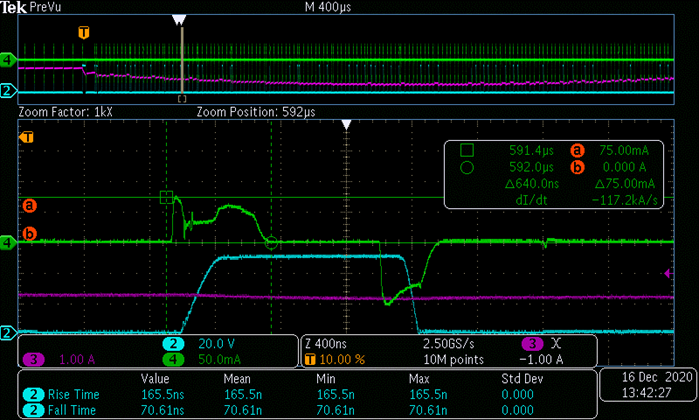

See attached oscilloscope screenshots from the same board:

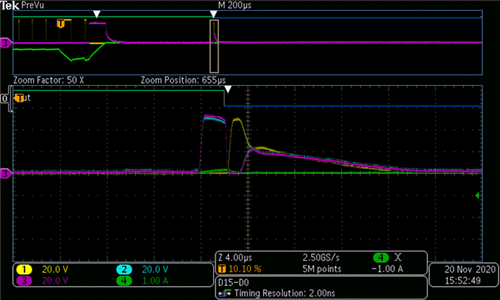

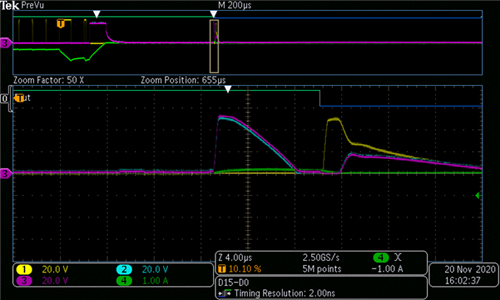

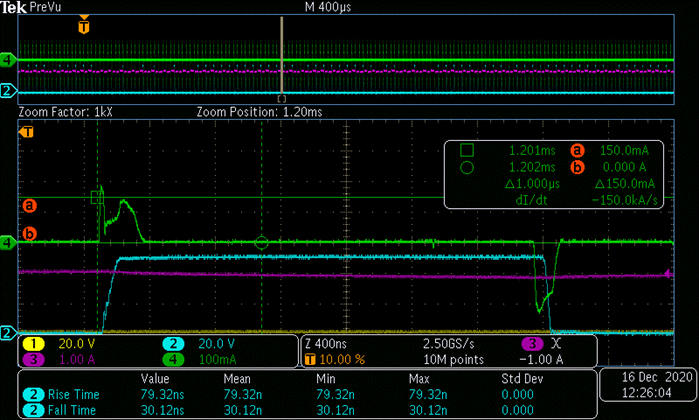

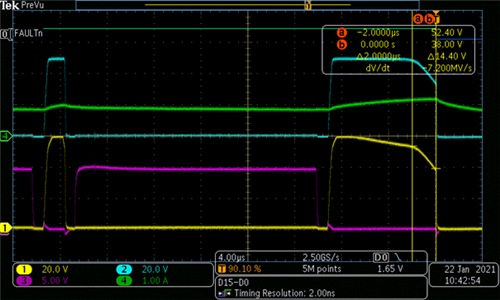

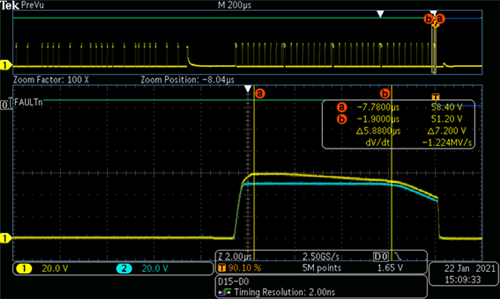

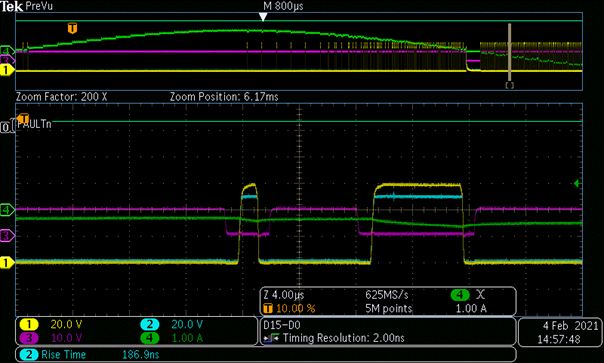

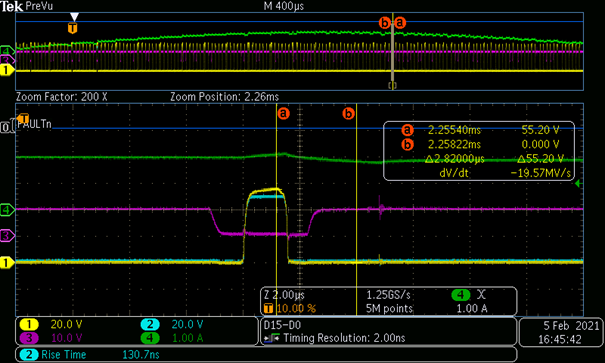

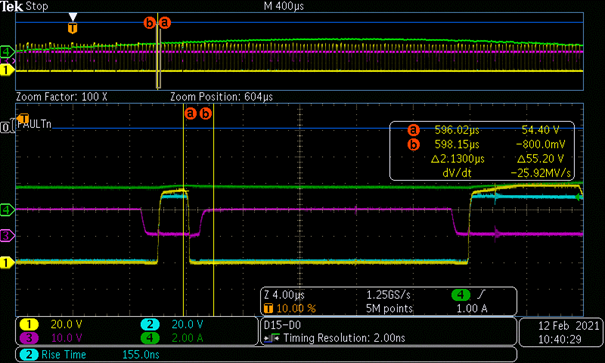

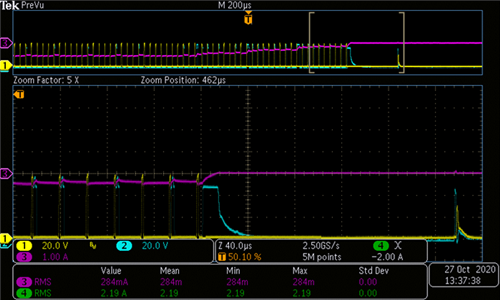

- X axis_Q24 MOSFET_bad DRV8711.png è rt=311ns

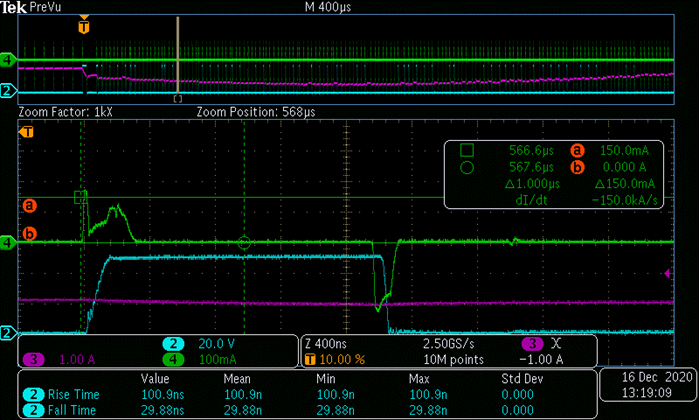

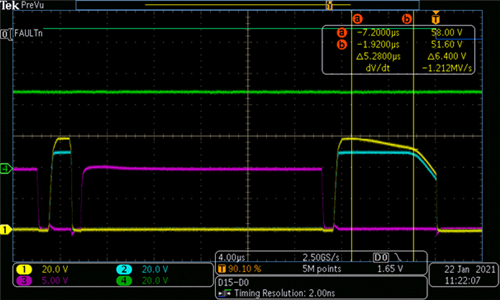

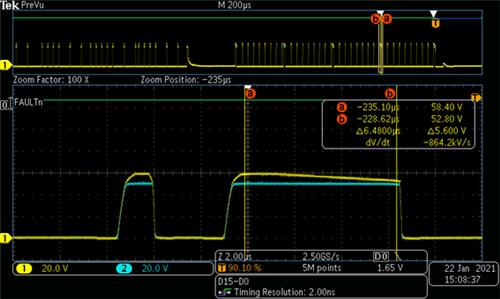

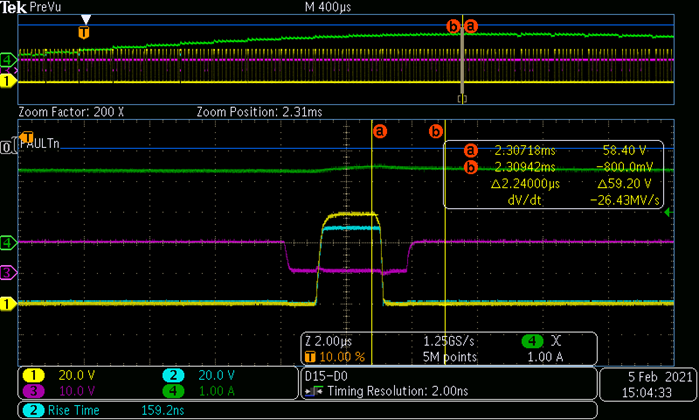

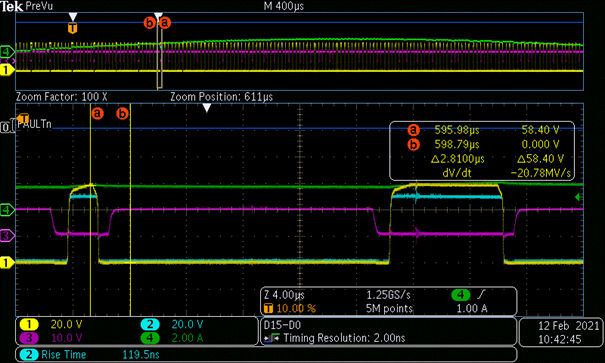

- X axis_Q24 MOSFET_brand new DRV8711.png è rt=165ns

How to explain the rise time has increased since the beginning of the life cycle?

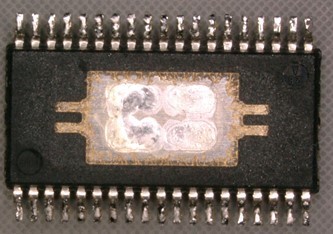

Below part marking of the DRV8711 concerned by the issue:

83TG4 CGLY (see attached picture 102X.jpg)

82TG4 CPYH (see attached picture 590X.jpg)

82TG4 CPYJ (see attached picture 763X.jpg)

Could you detail date code and numbering and confirm these parts are right?

Any suggestion, workaround, explanation?

Many thanks in advance

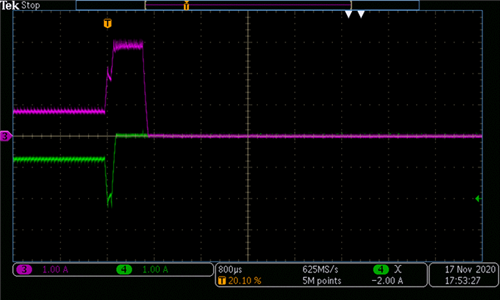

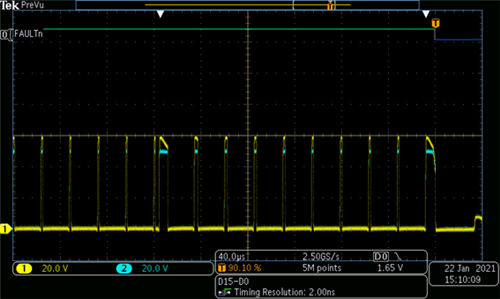

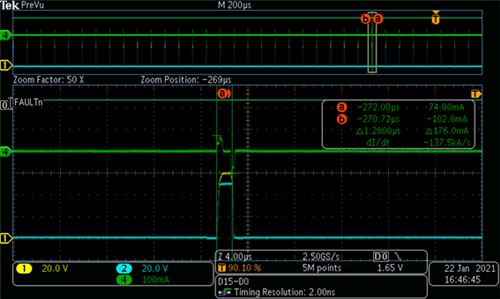

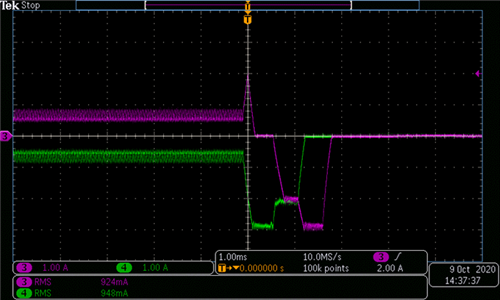

board n°1016 FAULTn when CH4 current rise positive

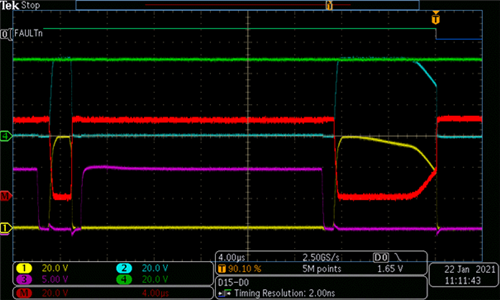

board n°1016 FAULTn when CH4 current rise positive board n°1152 FAULTn when CH4 current rise positive

board n°1152 FAULTn when CH4 current rise positive