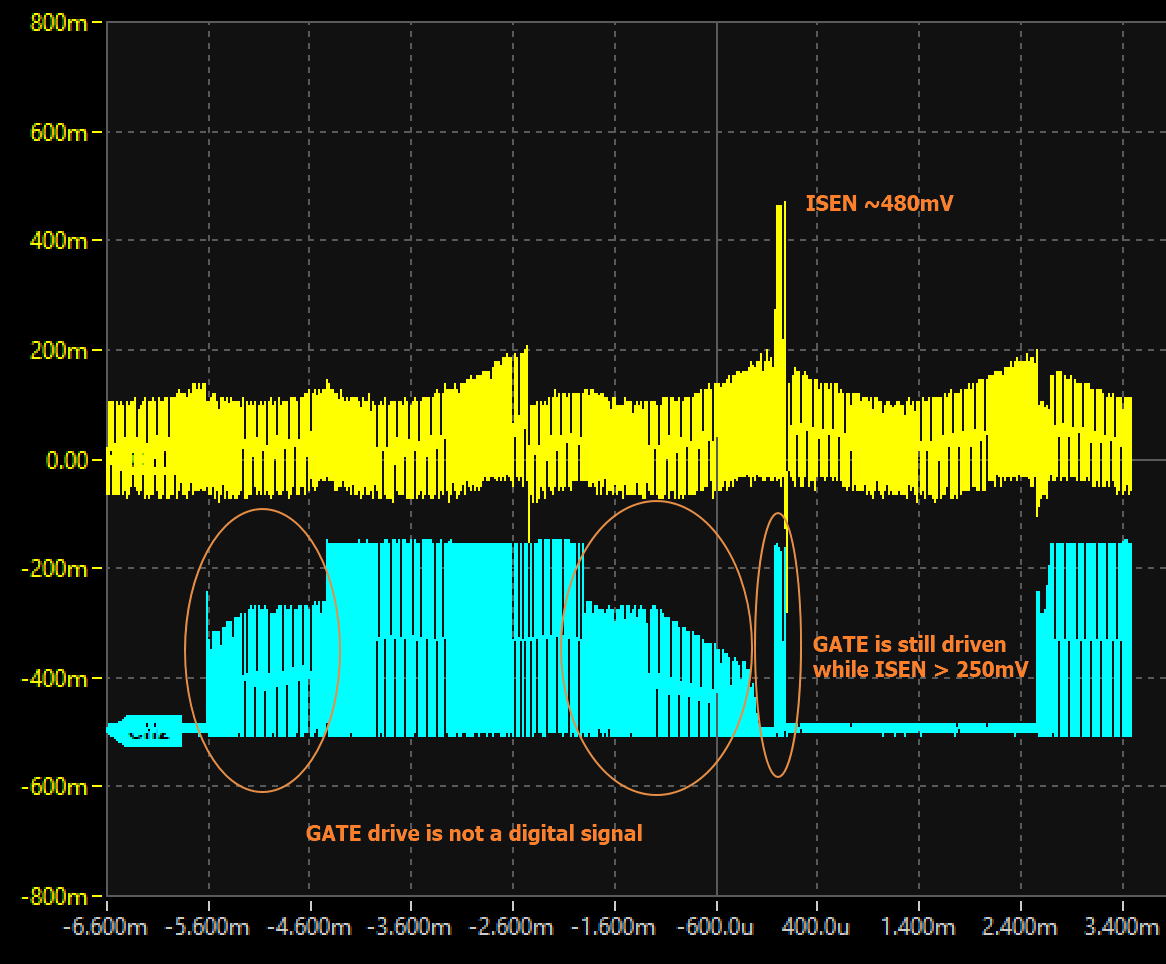

I am testing DRV8306 in a new design of ours and came across a strange behaviour. Based on cycle by cycle current limit feature, if at any time the ISEN goes above VLIMIT, all three upper FETs should be cutoff. But in my instance, I can see the ISEN ramping up to 480mV, but the upper FET is still being driven. This happens once per revolution.

Any explanations?

Also the Gate drive doesn't seem to be a digital signal.

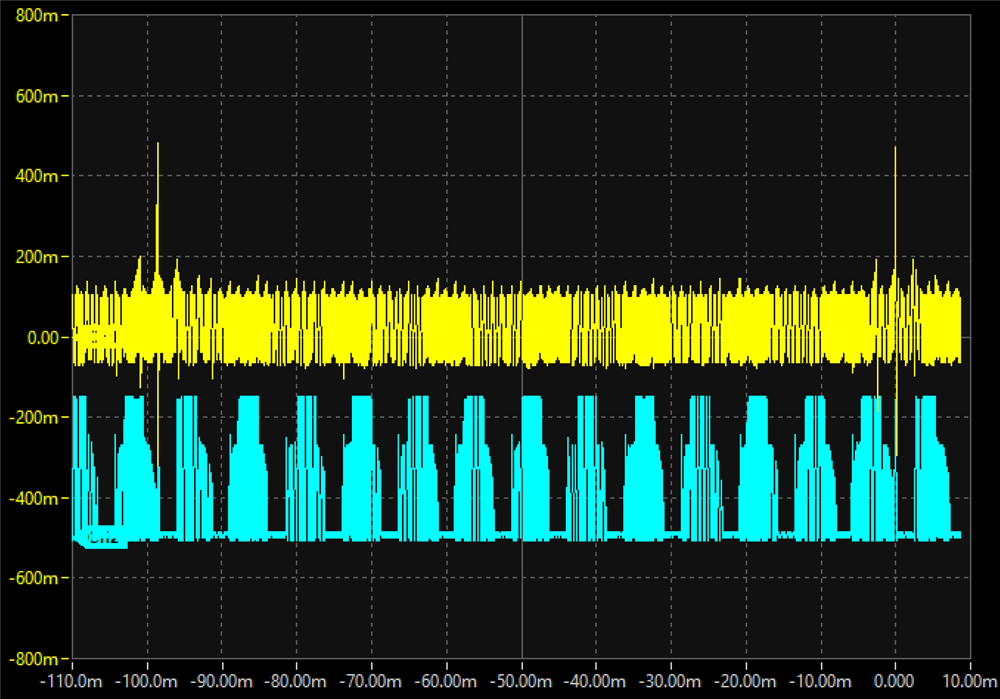

One full 10Hz cycle below.

Thanks,

Kay