Other Parts Discussed in Thread: TPS54061

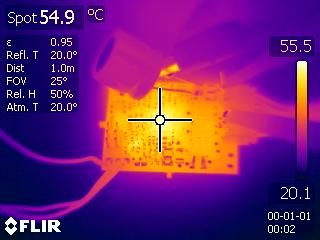

In my design a DRV8308 is driven by a microcontroller on a very compact 4-layer pcb.

The motor is required to spin from 400 to 7700 RPM open loop, and the speed reference

is entered through the speed register. The max current required by the motor during operation is <2A

and the board is supplied at 28Vcc.The +5V to the hall sensors and microcontroller are supplied

by a TPS54061 switching regulator. Mosfets used are NTMFD5C674NLT1G.

I use the internal clock generator.

I am having a hard time in having the motor spinning smoothly without tripping the faults on the driver.

In a couple of cases the DRV8308 burnt out for apparently no reason....

At the beginning of the speed ramp the motor is run with 3 hall sensors, then when the !lock signal goes low I move to

single hall 120° mode. Some questions:

1 should I limit the frequency I update the speed register (the speed reference on microcontroller comes from an analog input).

2)-How can I know if the speed increase/decrease is too steep? Should I control the speed slew rate? What is the

correct program flow when the !lock signal is lost because of excessive speed change or when the speed is too low to keep

the lock logic working?

3)- Is it correct to use the Syncrect bit on and the brkmod bit on in order to keep the

Bus voltage under control, avoiding that a sudden stops cause a surge on Vbus during

regeneration?

Thank you for your help.

Gian Paolo