Other Parts Discussed in Thread: DRV8323R, DRV8323, CSD, DRV832X, CSD18540Q5B

hi TI member

I have tested the DRV8323RS MOS GS Drive signal ,but i found that it is not a perfect square wave,

I have set the IDRIVEP_HS =80mA, IDRIVEN_HS =1640mA, if i set the IDRIVEP_HS more high, the GS waform will be oscillated;

so i have some doubts

1:what caused the waveform not the square wave ?

2:when VGS is set to low, why the Vgs valve is not till to zer ?

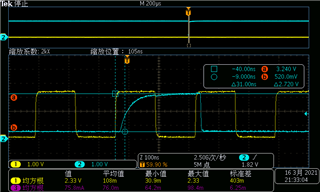

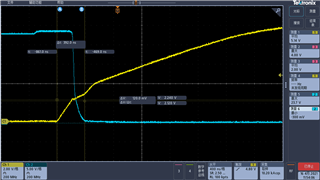

plz check the following pic ,this is the low-side Mos Vgs waveform;

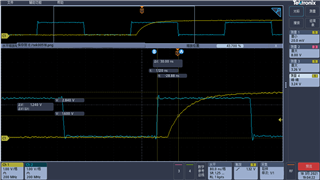

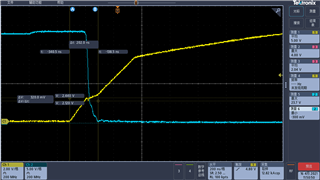

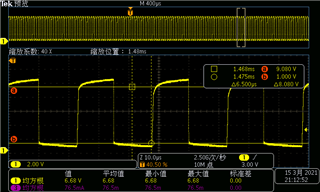

2: the following pic is the high-side mos drive waveform,

1: why the Vgs max voltage vibrate ? the vol ranges 10.6~11V ,which is not fixed

pls help me ,thanks