Part Number: DRV8353R

Other Parts Discussed in Thread: DRV8353, MOTORWARE, OPA835, DRV8343-Q1

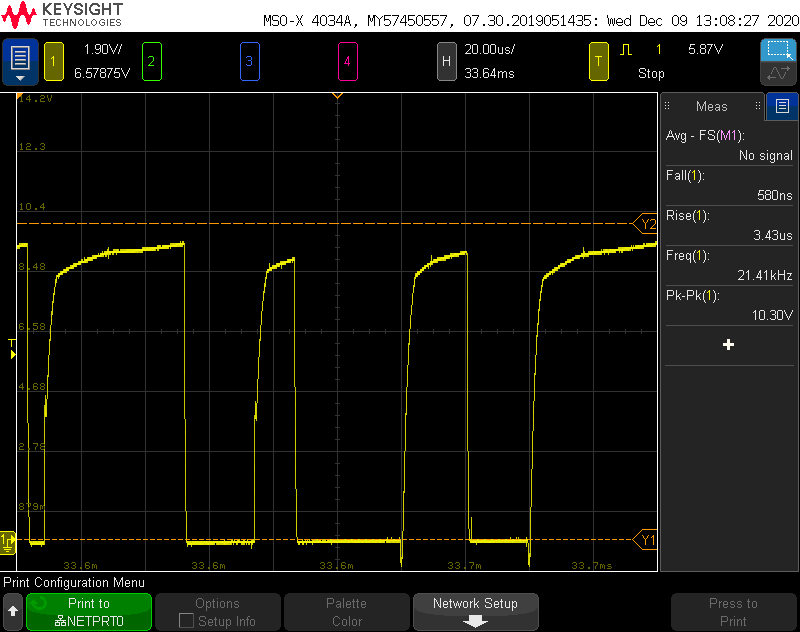

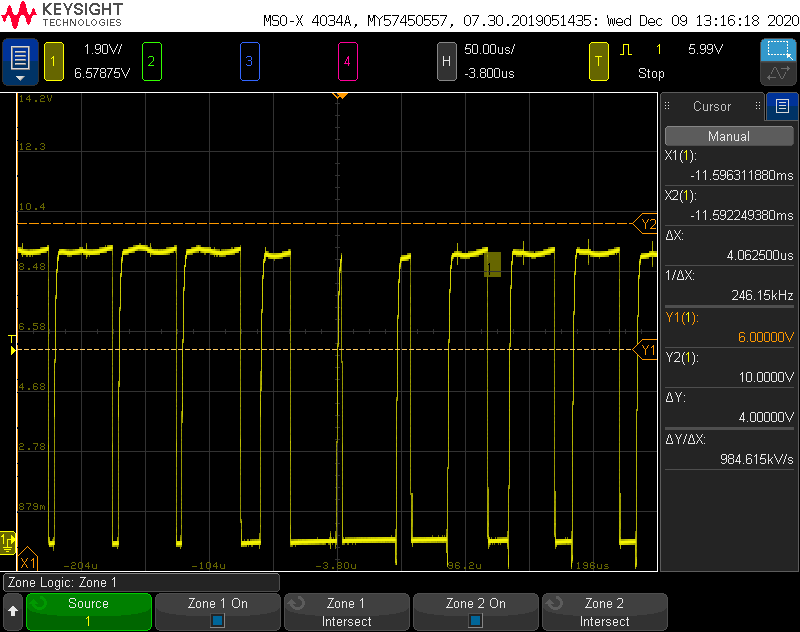

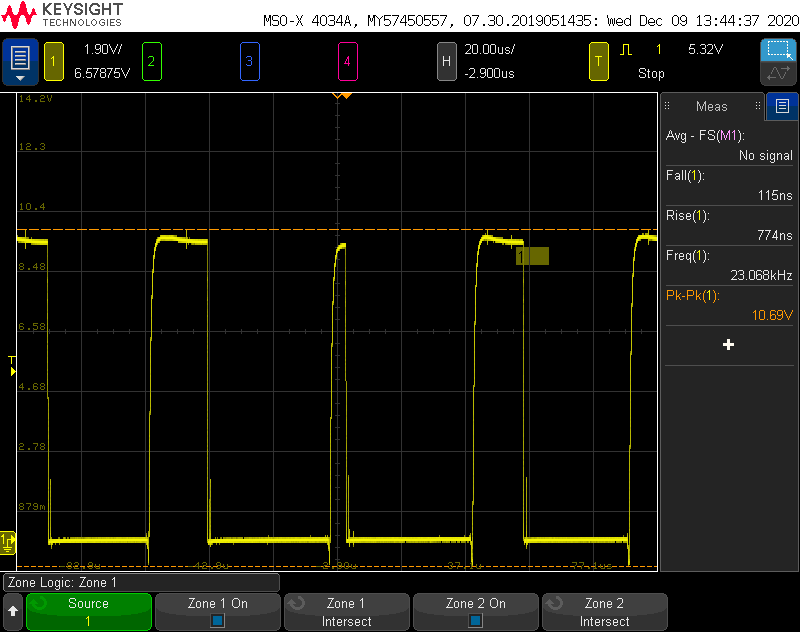

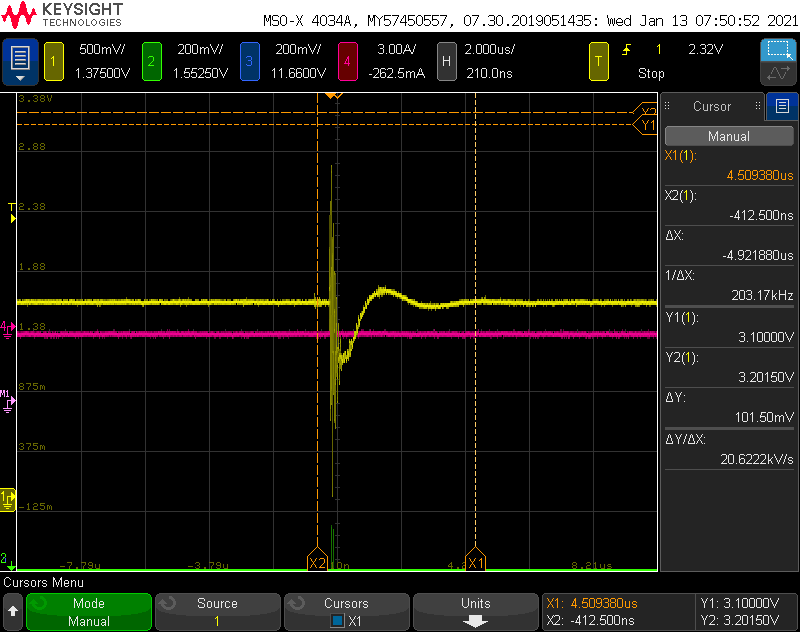

We are working on debugging the first revision of our own custom hardware. We have largely copied the DRV8353RS-EVM (same values for current filter, voltage sense filter, VCP cap, CPH/CPL caps). We are seeing an issue where when the motor RPM gets to around 90% of the Max motor RPM for a given voltage (happens at any voltage from 24V-45V VM), we start to get chattering in the motor and start to lose control. If I increase the voltage on the power supply a few volts, the chattering goes away. The FET gates all look good up to and beyond this point. The charge pump voltage also looks good.

Layout is done on a 6 layers with nearly all feedback signals running perpendicular to high current paths and generally sandwiched between stitched ground layers. DRV8353 layout was copied a directly as possible from EVM. This occurs on an unloaded motor and at low currents. I am curious if anyone else has seen this type of issue or has any ideas for next steps in terms of troubleshooting.

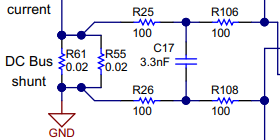

Rshunt = 2x 3mOhm in parallel (1.5 mOhm) @ 20 gain (USER_ADC_FULL_SCALE_CURRENT_A=110A)

FETs = 2x IAUT300N10S5N015ATMA1 (330 nC total Qg with 2 in parallel)

Idrive (HS/LS) Source = 1000mA

Idrive (HS/LS) Sink = 1800mA

USER_PWM_FREQ_kHz = 20 kHz

USER_NUM_PWM_TICKS_PER_ISR_TICK = 1

USER_NUM_CTRL_TICKS_PER_SPEED_TICK = 20

USER_NUM_CTRL_TICKS_PER_TRAJ_TICK = 20

Motor L = 280 uH

Motor R = 0.2 mOhm

Motor Pole = 3 pole pair