Other Parts Discussed in Thread: UCD3138, UCD3138064,

Hello,

I am using UCD3138ACCEVM149, ready to drive a LLC circuit.

I modified the demo program from trainingLab 3.

by changing the cpusample value, i can see the output PWM signal changing from 500KHz to 2MHz, that is working as I expect (PWM0 module).

while the problem is

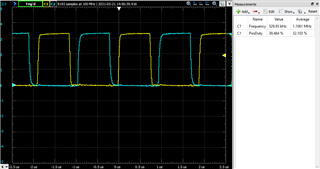

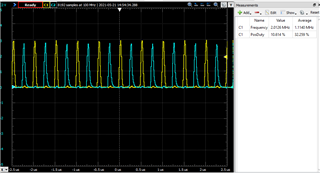

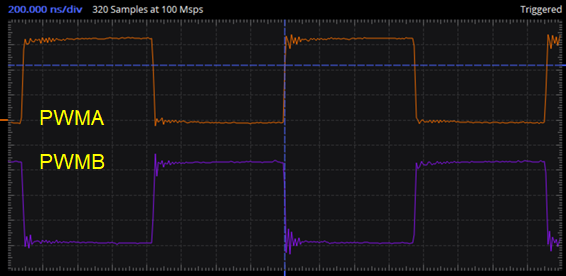

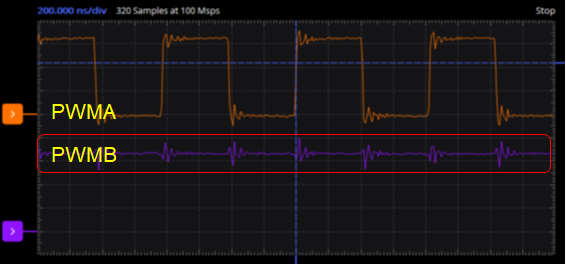

PWM0A pin is always good,

but the PWM0B sometimes is good, some times is HI level.

I mean during the frequency of 500kHz ~ 2MHz, Pwm0B is good at some frequency, but output HI level at some other frequency.

I am confused,

would you please give me some advices on what could be the reason of it?

thanks a lot!

Xioafeng Wu