Hi

As a continuation to the previous query

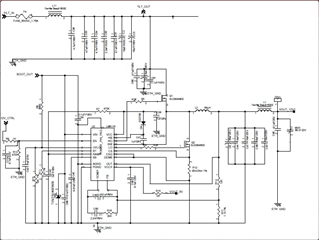

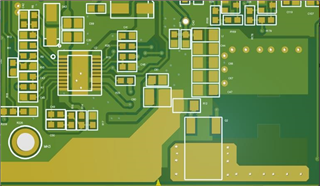

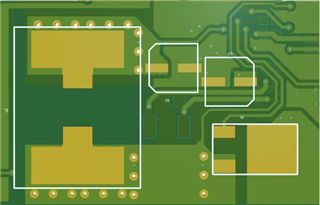

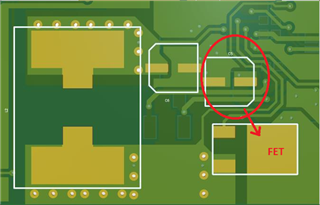

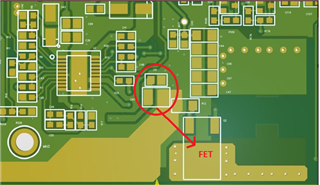

"We have used LM5116 PMIC to output 14.4V/3A from max input of 60V in our product design.

PMIC is repeatedly failing with failure mode of output 0V. When debugged Pins HB, HO,SW Impedance always found to be low [some cases shorted to GND potential]"

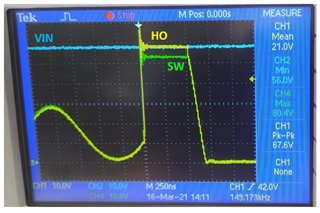

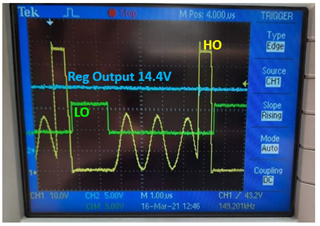

We have waveforms of a partially failed LM5116 IC [found HB and SW pin with low impedance than expected]

All signals measured wrt board GND potential [14.4V regulated output, VIN, VCC, SW node pin]

Attached the waveforms.

Please revert back on the possible failure mode