I want to use two TPS2663X eFUSEs for priority power muxing of two 28VDC supplies.

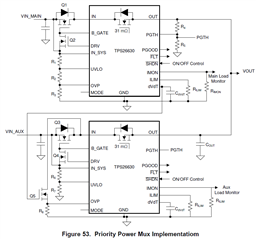

In section 10.3.2 of the data sheet the following is stated "The TPS2663x devices provide a simple solution for priority power multiplexing needs."

However, when looking at Figure 53, I can see that the OVP pin is required, which is only present for the TPS26630 and TPS26631 devices.

This must mean that priority muxing is not supported by the TPS26632/TPS26633/TPS26635/TPS266336?

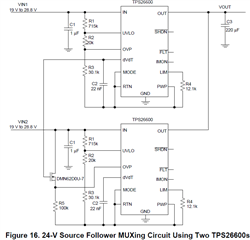

This is also what I can gather from application note SLVA811A - "Power Multiplexing Using Load Switches and eFuses", Figure 16.

Can you please explain the working of the circuit in Figure 53?

How should the resistor R8 be calculated?

Regards Lars