Other Parts Discussed in Thread: UCC28730

Hi E2E,

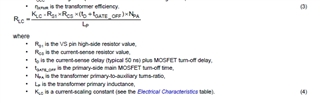

Figure 15 shows the four regions of operation. In region 3 the switching frequency is held constant (25kHz) while the peak current in the switch at turn-off is controlled from 25% to 100% of its maximum. In this region, our customer converter displays have some low-frequency oscillation in Vout (200mV p-p sinewave on +12Vdc with frequency ~500Hz).

Does stability in this region rely on the down-slope of the signal at Vs (pin 6) during the magnetizing reset time of Fig 14? If "yes", what is the range of slope to ensure good stability?

Regards,

Carlo