Other Parts Discussed in Thread: UCC27531

Hi!

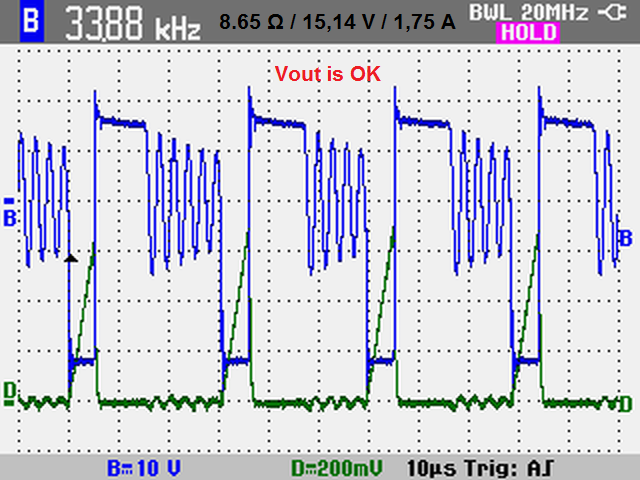

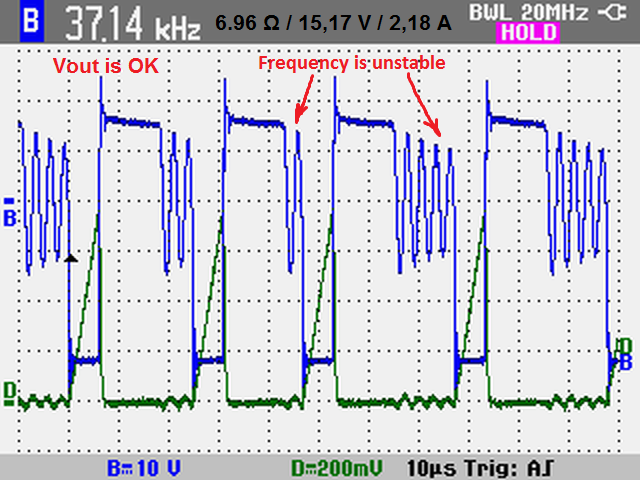

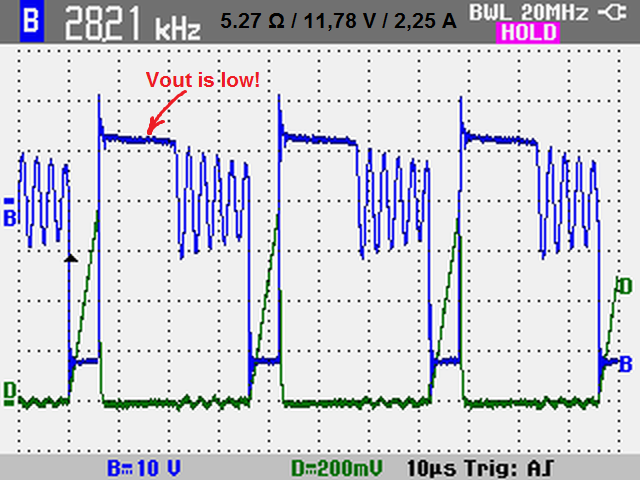

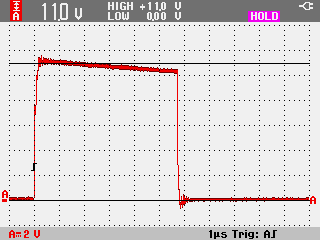

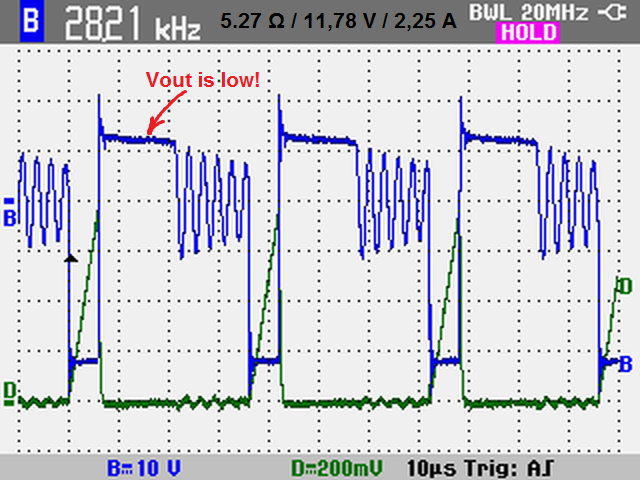

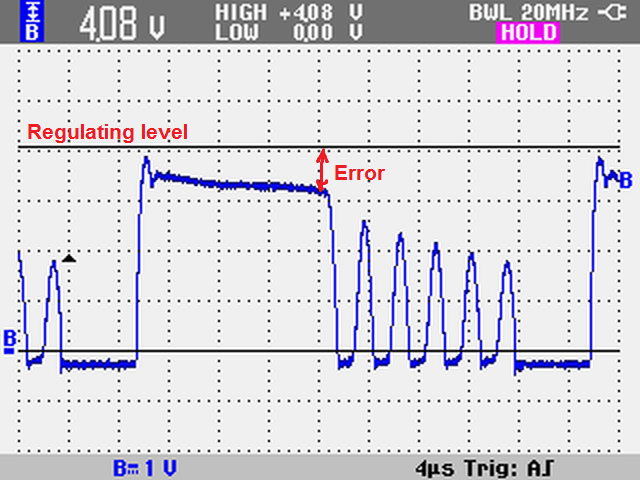

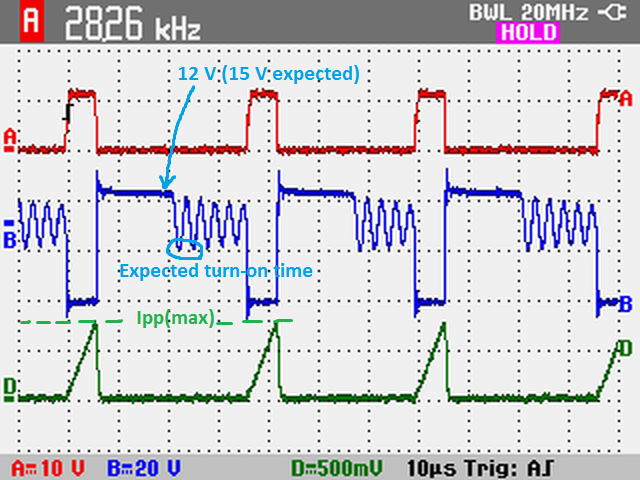

I designed 50 W flyback with 15 V output voltage. I have got quite a good regulation at loads up to 33 W. But when I connect extra load (total of 44 W) the power actually decreases as decreseses switching frequency and output voltage. Please see the waveforms (Red - Gate signal, Blue - Vaux voltage, Green - Vcs signal).

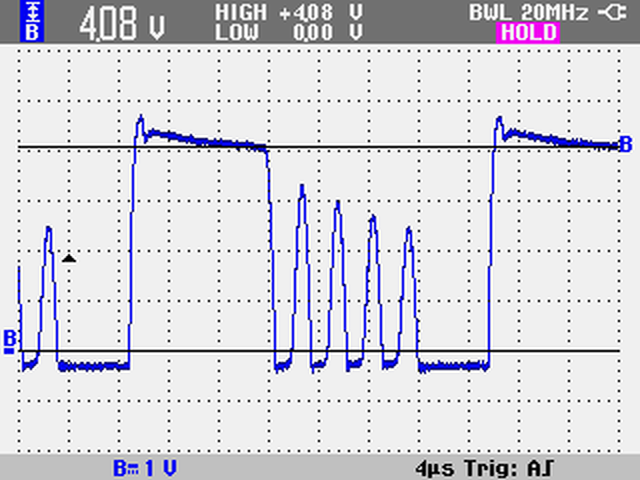

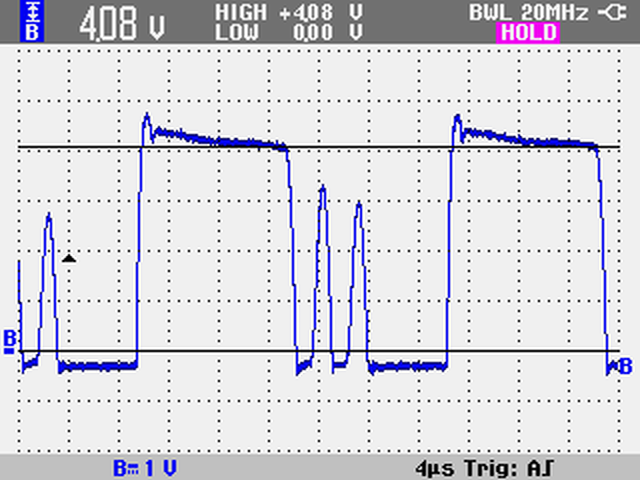

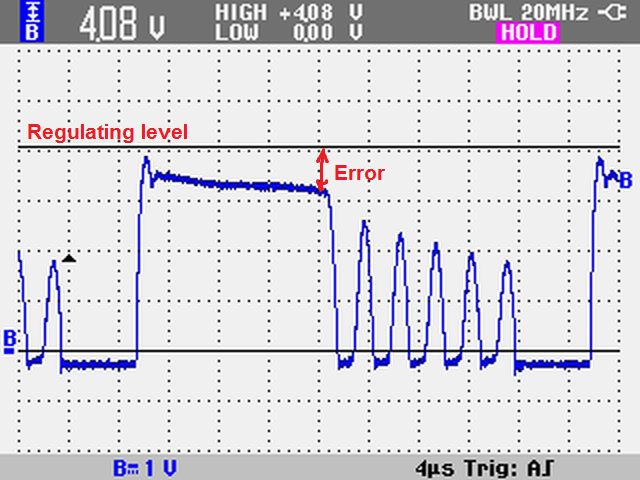

Secondary winding has the same number of turns as aux winding. So Vaux is close to Vsec. As you can see (blue waveform) Vaux = Vsec is approximately 12 V. In my design Rs1 = 50 k, Rs2 = 18 k. So voltage at Vs pin should be 12 * 18 / (50 + 18) = 3.18 V (much less then expected 4.05 V).

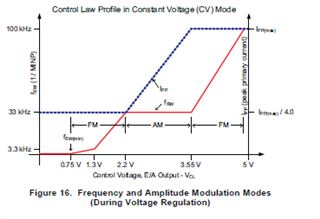

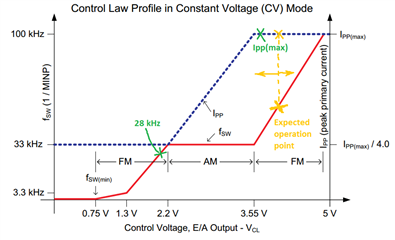

The Vcs signal has a magnitude of 0.75-0.8 V corresponding to Ipp(max). And the output frequency is set to approx. 28 kHz. Note that at lighter load (6.8 Ω) I get higher frequency than at higher load (5.1 Ω).

The question is why the frequency is reduced after connecting extra load? As I understand while Vs pin is below regulating level of 4.05 V the output signal should be switched at the first or maybe second valley (Expected turn-on time at blue waveform) and frequency should increase as well as output power. According to control law frequency can NOT be below 33 kHz while current is maximum.

The question is what exactly prevents UCC28711 from increasing the frequency? Or maybe what prevents UCC28711 from switching at the first or second valley providing at least 40 kHz and enough power to keep voltage at 15 V.