Other Parts Discussed in Thread: LM5060

HI,

We are working on a automotive solution and have used LM5060 as OVP sw with high side protection.

What I am seeing is as soon as the devices passes UVLO limit the timer capacitor charges to 5.4V and remains there- EN, UVLO, PGD and OVP are all in valid condition.

I tried to reduce the slew rate by adding caps on GATE drive pin (100nF) and adding total 200nF on TIMER pin but the situation remains same as it is.

Can you please let me know what should I do?

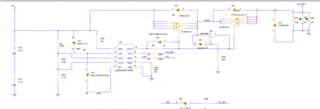

Below is snapshot of the circuit- (please note that UVLO and OVP pins are swapped in this symbol here which is corrected in system)

Thanks!

Mandan