Dear TI Team,

I have set the DDSG and DCHG outputs to be Active High outputs driven by REG1. Here are the issues I have been facing:

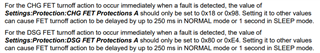

Issue 1. Upon SCD Fault trigger I have noticed significant delay in DDSG signal to trigger and go high as in the image below. In the scope image, Red spike is the current going beyond SCD threshold and then falling back quickly, however there is a significant delay in the blue channel (DDSG) to go high (approx 500ms). This will cause significant issue in stacking two ICs since the lower IC sensing the current will provide a delayed SCD or OCD signal though DDSG pin to external MOSFET driver.

I have used the following Switching Circuit with a PMOS for the DFET off path as described in the TIDA

Issue 2. DCHG pin toggles once (goes low) for a small amount of time when the DFETOFF pin (configured active low input and BOTOFF) is toggled to high input to turn ON both mosfets.

Please help me out with both of these issues.

Thanks and Regards

Manuj Agrawal