Hi ,

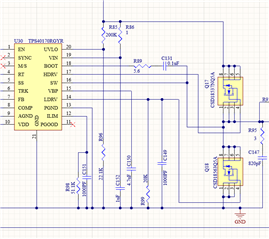

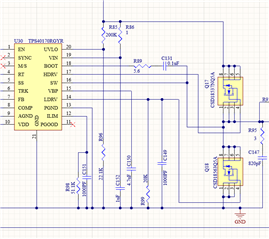

In what condition a "shoot-through" scenario could happen on this configuration that could damage either the high drive or low drive FET?

Thank you.

Jojo

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi ,

In what condition a "shoot-through" scenario could happen on this configuration that could damage either the high drive or low drive FET?

Thank you.

Jojo

Hi Tim,

Thank you for your reply. Is there a reason or other purpose why 1 Ohm resistor exist on TI data sheet? Or it's just for layout flexibility? Or it's been explained before during our previous reviews that I might not able to catch.. Another thing , can we say that TPS40170 have internal shoot through protection not just written from the old data sheet? And last but not the least, regarding the control mechanism we're employing an external micro via VPROGClamp injection control signal to the FB control pin, bypassing the normal output feedback loop, could this cause a potential un-stability that may lead to shoot-through condition that may damage the HDRV or LDRV FET when it enters a burst mode region.

Thank you.

Jojo

Hi Jojo,

The gate drivers are designed not to overlap for all conditions, independent of control. However, if the SW voltage has a high dv/dt, it can capacitive couple into the low-side gate and cause a blip during the Sw transition (this is the case for all buck designs). So just ensure that's not evident on the low-side gate (the spike on LDRV should definitely be kept below the Miller plateau voltage of the FET, hence the cap from LDRV to GND that changes the capacitive divide ratio from drain to gate),

The 1 Ohm was originally intended for Vin ripple filtering, but my understanding is it may cause an RC delay wrt high-side current sensing -- this is for failsafe current limit (the main OCP function is using the low-side FET).

Regards,

Tim