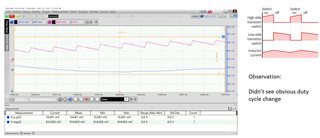

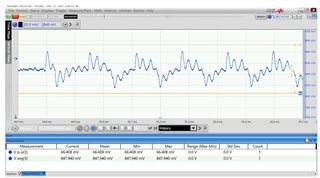

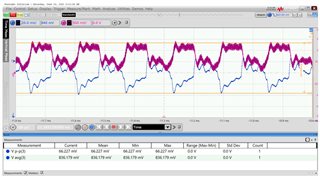

We designed this part TPS546D24 in our PCIe card outptut ripple is very high - 0.8V@8A load the ripple is about Vp-p= 90mV. Ripple current is +/-3A. Due to this we cannot run the processor at higher speed & higher load. We need you to verify that we have the design the TPS546D24 correctly for least ripple.

Vout = 0.8V

I out = 20A max

I out trans = 10A max

Fsw = we have selected 900KHz but we can change this for least ripple.

C out = ~ 2000uF

Inductor = 0.3uH with 32A current & max DCR=1.1mOhms -- ASPIAIG-F1040-R30M-T

Regards,

Farooq (408-482-2315)