Other Parts Discussed in Thread: LM25117

Hi, I’m starting using your LM25117 buck controller.

I need to understand how design the resistors in series with the power mosfets.

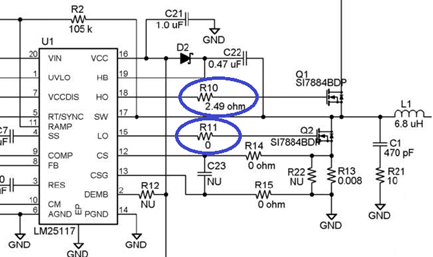

In your demboard «AN-2112 LM25117 Evaluation Board» the schematic is the following

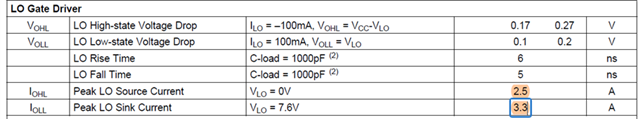

The driver currents in LM25117 datasheet are

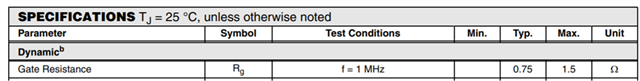

The internal resistance of the mosfet SI7884BDP in its datasheet is

The low side mosfet is considered ( Rgate_external = 0 Ohm).

In my opinion, the driver peak current is

I_driver_peak = Vcc / (Rgate_internal + Rgate_external ) = 7,6 V / (0,75 Ohm + 0 Ohm) = 10,1 A

That current is very high compared with datasheet maximum driver current.

If R_gate_external = 2,7 Ohm is used, the peak current is

I_driver_peak = Vcc / (Rgate_interna + R_gate_external) = 7,6 V/ (0.75 Ohm + 2,7 Ohm) = 2,2 A

In my opinion R_gate_external = 2.7 Ohm is ok.

My questions are:

1) There is something wrong in the demoboard low side mosfet design ?

2) My design method is correct ?

Take into account that the buck converter is used in a very important PCB for my company, so the most important thing is the reliability of the circuit.

p.s. I think that in the demoboard, the high side mosfet total gate resistance is higher than the low side mosfet one to reduce the voltage ringing on the switching node, it is correct ?

Thanks.