Other Parts Discussed in Thread: TDA4VM, MSP432E401Y, TPS22965

Hi TI Support Team

We use LEOA (TPS65941212)+LEOB(TPS65941111) for customer board for TDA4VM design.

One issue finding when we do the power cycle test: (Battery Power on / Battery Power off ......) about every 2 second one cycle.

Sometimes the LEOA buck can not ouput VDD_CPU_AVS (0V8) voltage, The issue happen frequency about 1 /10 times.

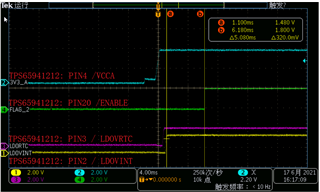

We confirm the VCCA / ENABLE / LDORTC/ LDOINT output voltage correct.

1. Do you know in any condition the LEOA buck can not output correct voltage?

2. How to check which error detection to stop the buck power-up from LEOA?

3. Do you have timing requirement for VCCA to Enable ? Currently we have 10ms from VCCA to Enable.

4. Any suggestion for this issue.

Customer board test result:

Thanks

Yutai