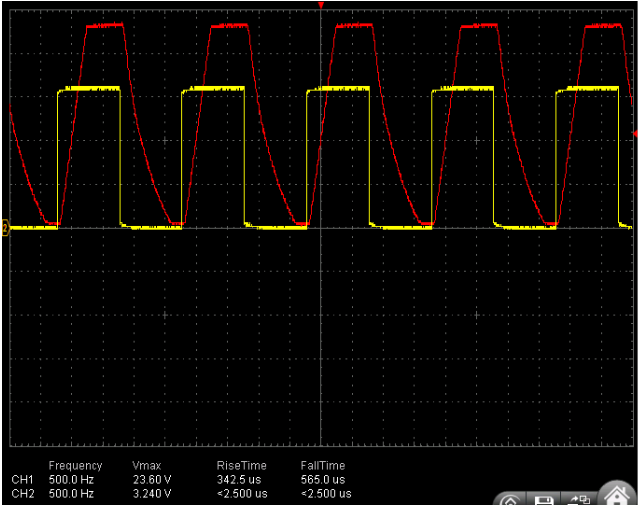

We are using TPS274160BRLHR in our industrial digital output design, We observed that output put raise and fall times are at maximum (around 330ms) when we check the output using DSO.

Is there any way to reduce the raise and fall time?

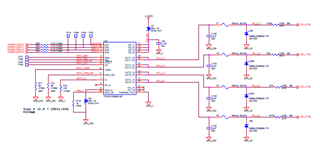

We have Zener, TVS and series resistors at the output, those are influencing fall time.

But raise time should be around 130ms while operating @25C.

We are trying to switch 24V output at 500Hz.

Please help me solving this issue