Hello,

I have some questions about schematic and board layout with TPS61240.

The TPS61240 that I use for my project didn't work property.

I assumed the problem is a board layout, So I updated the layout.

Could you review my schematic and board layout to prevent same mistake?

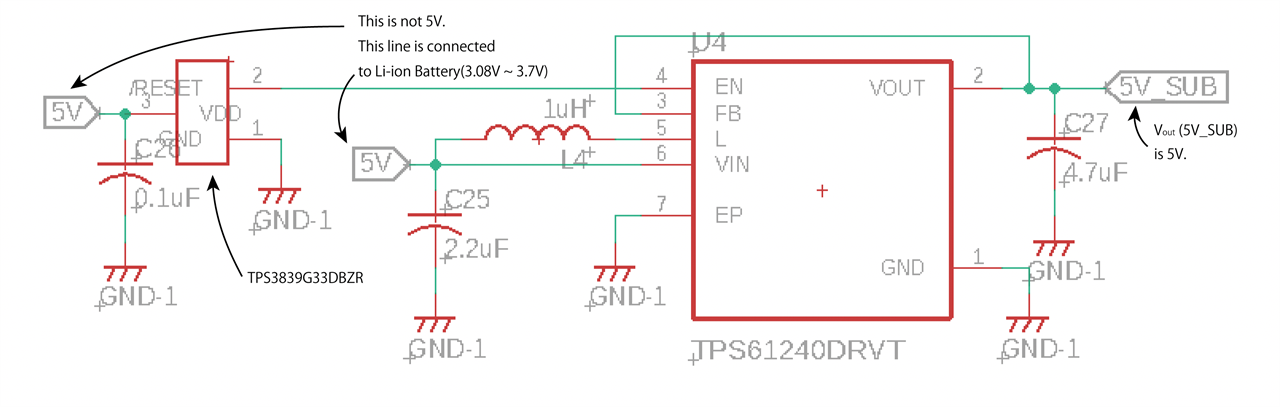

This is my schematic(fig1).

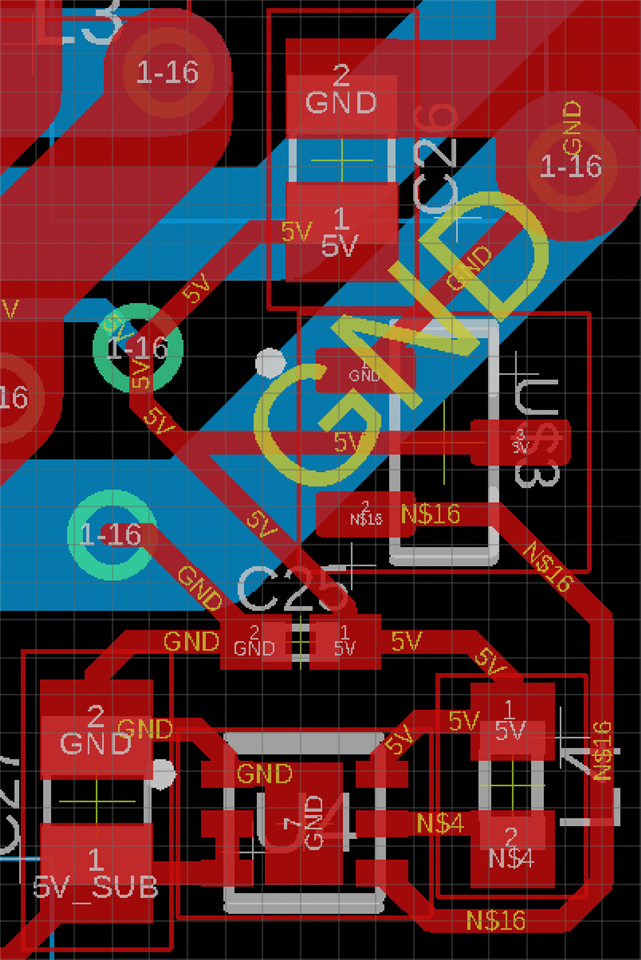

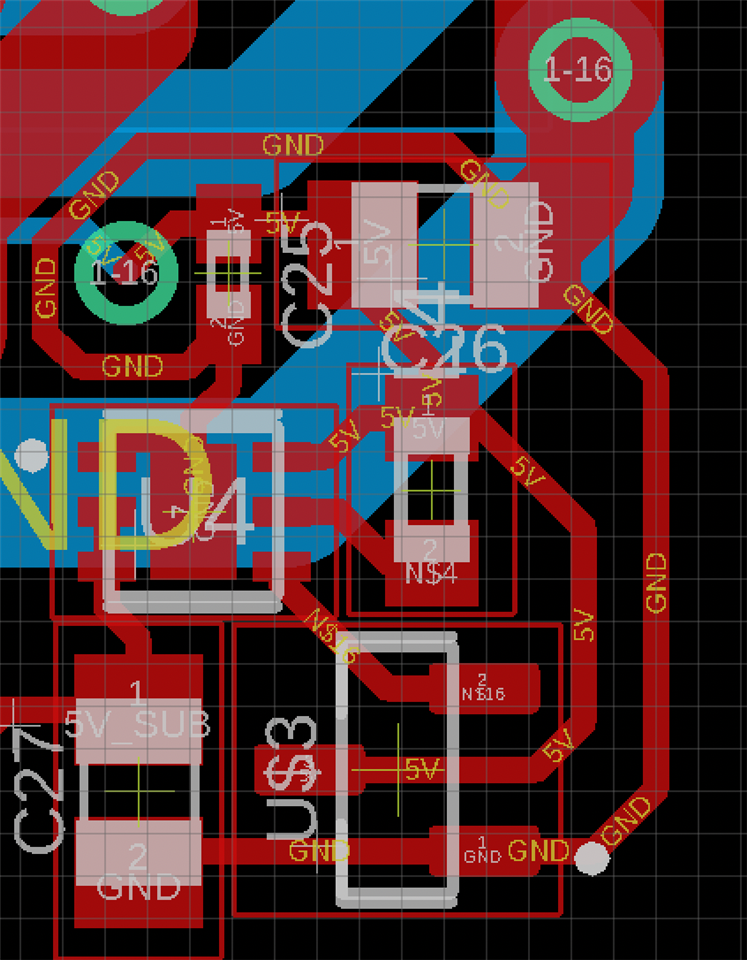

This is my board layout(fig2).

And if possible, Could you tell me where are no good in old board layout?

Old board couldn't step up voltage to 5V. It outputs 1.8V with huge ripple.

(Video URL : https://drive.google.com/file/d/1sYtx5l7J-lXN0-zgC8fz_RvAY9YLiDL9/view?usp=sharing)

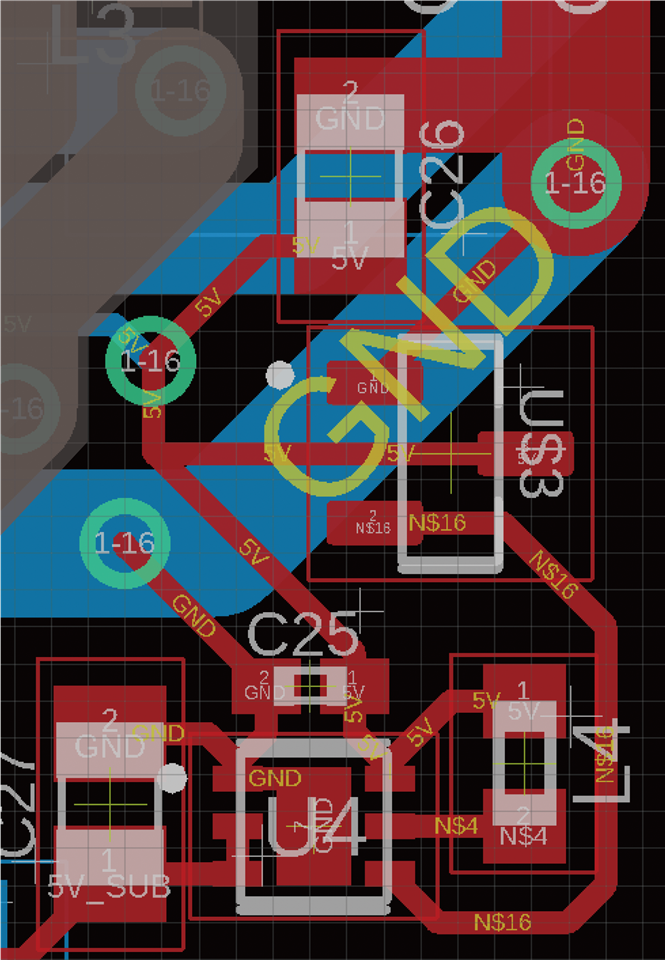

Old board layout(fig3).(Schematic is same.)

Thank you.