We are implementing a custom design inspired from Beagle Bone Black.

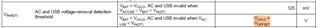

To avoid the brownout issue, we have implemented a circuit with voltage supervisor + load switch, and are facing issues during startup from external power supply.

To debug this issue, we are now trying to better understand the working of PMIC on batteryless applications.

Currently, we have removed the voltage supervisor and load switch from circuit, and applying external power supply directly to the PMIC input.

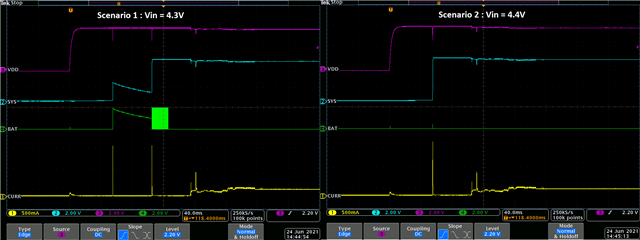

Can you please explain the differences between the below two scenarios?

Scenario 1 : Vin = 4.3V

Scenario 2 : Vin = 4.4V

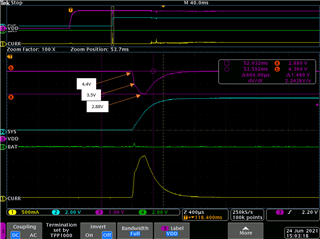

Question is, why is the SYS voltage not building up to full 5 V in one case, whereas it is building up to 5V in the other case?

With the voltage supervisor connected, this phenomenon of retry is worse. Hence we are looking to understand why this is happening in the first place.