Other Parts Discussed in Thread: OPA172

Hello,

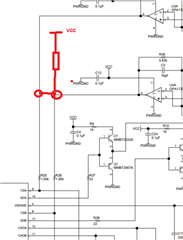

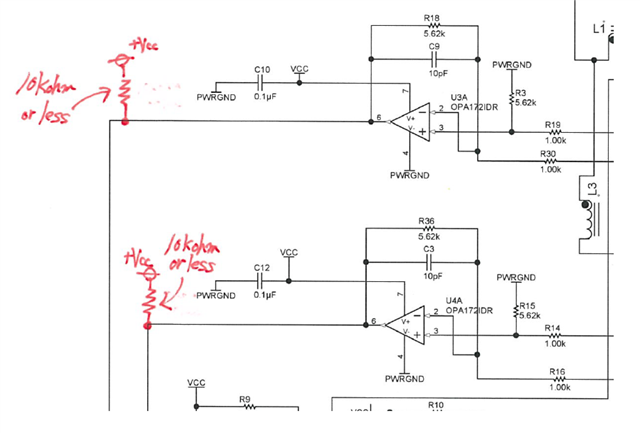

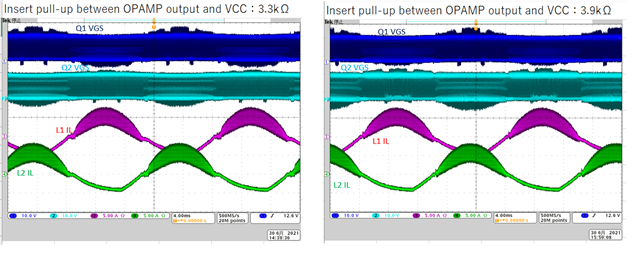

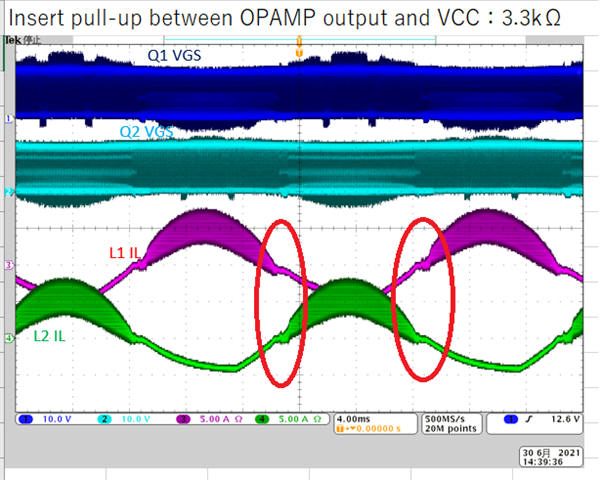

I have verified the operation of the bridgeless circuit of UCC28070, but confirmed the strange operation.

I have put together the questions in the attachment, so please let me know what you think.

Best regards,