Hi All,

I would like to ask a question on TPS54310.

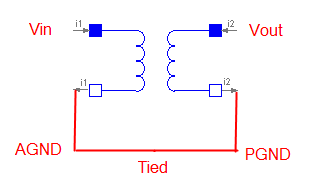

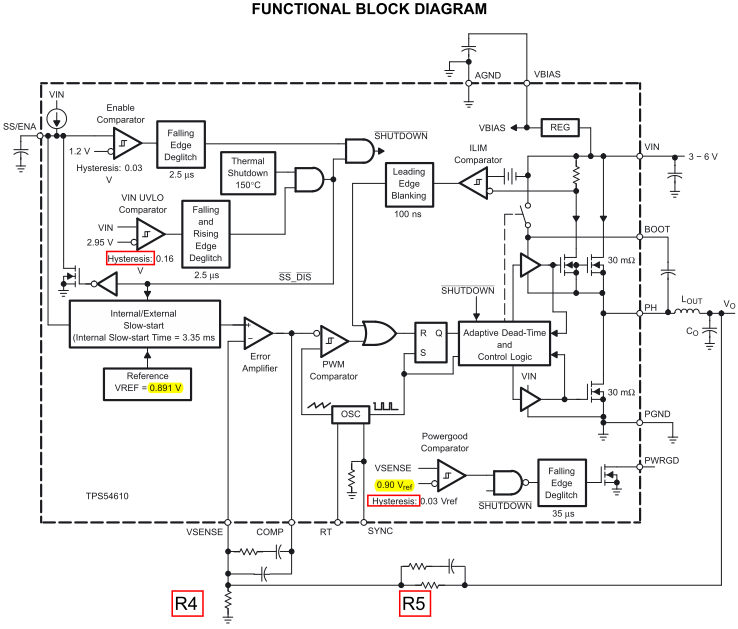

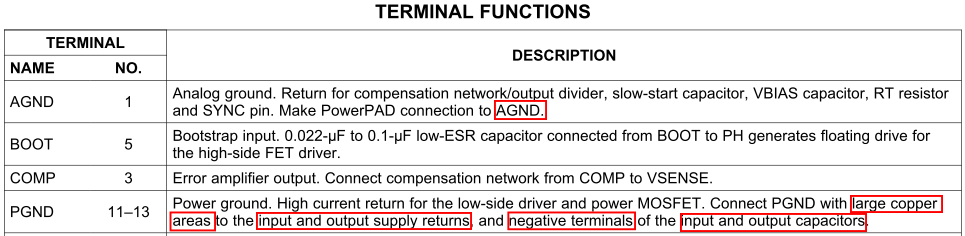

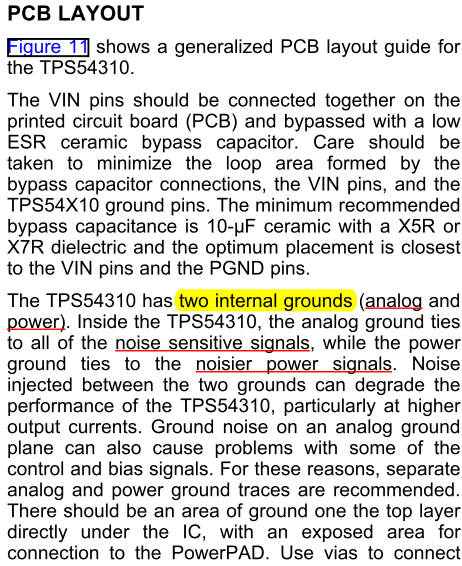

There seems to be two ground: analog ground and ground here. But in the PCB layout I see they are actually all tied together. Why?

And on page 9, PCB Layout, internal analog and power grounds are said to have different functions and are connected to different (noise sensitive signal, noisier power signal). But since in PCB layout the two grounds are physically tied together, how can they differentiate then who is tied to noise sensitive signal and who is tied to noisier power signal?

Thanks,

Zheng