Hi

We have used UCC21750 to switch our Synchronous Buck MOSFET

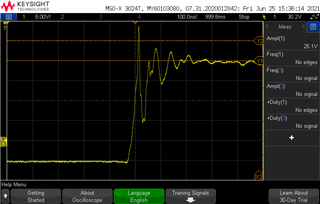

We are getting under shoot in the gate pulse of top MOSFET as the below image(Fig:1)

Fig:1

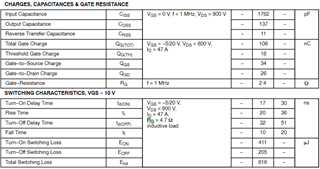

We have used 1E for RON and 0.3E for ROFF

Our Mosfet details in (Fig:2)

Fig:2

Need your support to solve this issue

Please share your mail ID to take this conversation as a personal conversation