Other Parts Discussed in Thread: TPS51200, , ALP

Hi everyone,

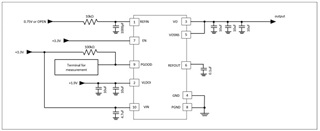

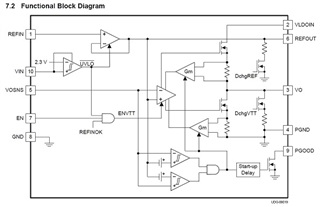

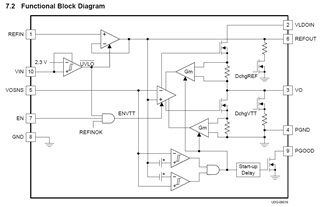

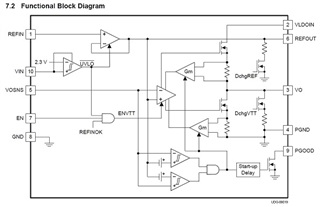

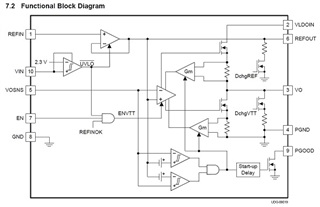

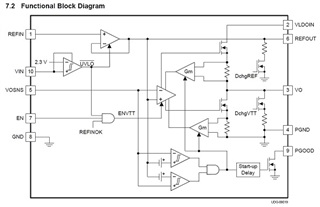

I use the TPS51200QDRCRQ1 device as the VTT regulator, that has 0.75V input at REFIN and 0.75V output from VO and REFOUT.

However, some boards were not worked correctly, even though same circuit has been build on every boards.

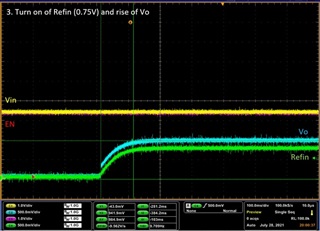

The problem phenomena is same, the 0.75V was input at REFIN but 0.75V was not output from VO and REFOUT.

The OUTPUT of VO and REFOUT showed about 1V.

We do not think that that problem would be caused by the circuit.

Because the circuit is made as recommended circuit in the Datasheet, moreover there are some boards that worked correctly.

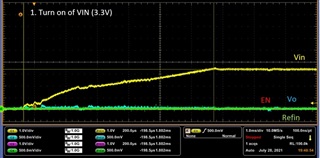

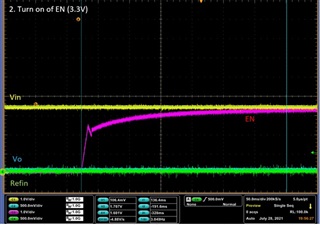

But we think that that problem might be caused by the input sequence of the REFIN/EN/VLDOIN/VIN pins.

About the input voltage sequence of the REFIN/EN/VLDOIN/VIN pins, we are understanding that there are no limitation.

But that problem might be occurred by resistance characteristic different of each boards, that means that problem would be caused by the input sequence difference of every boards.

So we would like to confirm that how should be set the TPS51200QDRCRQ1 device's the sequence of input voltages as the recommend condition.

Would you please answer about the recommend input voltage sequence for TPS51200QDRCRQ1 device.

Thanks and Besr regards,

Kura