Dear Team

Could you please help to review customer's layout?

The layout file as attachment.

Many thanks

Denny

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Dear Team

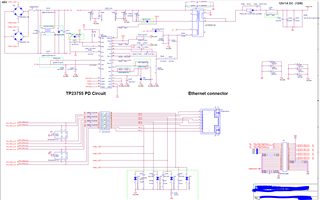

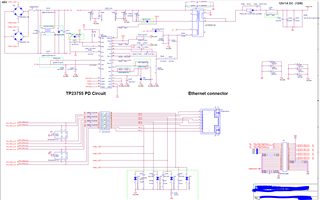

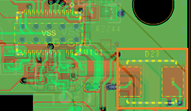

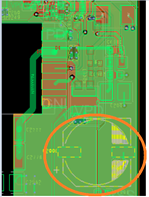

Could you please help to review customer's layout?

The layout file as attachment.

Many thanks

Denny

Hey Denny,

I will review layout no later than EOB Tuesday.

If this post answers your question, please indicate so by marking this thread as resolved. Thank you.

Regards,

Michael P.

Applications Engineer

Texas Instruments

Hey Denny,

Here are some comments on the layout:

- D29 needs to be as close to the IC as possible. it should also have at least two vias per pad

- the input power path is not optimized. The IC is on the opposite side of the board as the input. This is not preferred power path. The IC should be on the side of the transformer as the RJ45 input. We do want the IC pin DRAIN to be as close to the transformer as possible to minimize this path. It appears this is done. But we must also work to reduce the input power path in general.

- the input bulk cap should be closer to the IC as well.

- the drain path is too narrow. The entire primary side current is flowing through this trace, it should be bigger.

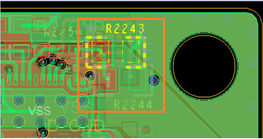

- Both RSNS resistors should have more vias

If this post answers your question, please indicate so by marking this thread as resolved. Thank you.

Regards,

Michael P.

Applications Engineer

Texas Instruments

Hi Michael

Thanks you recommend, the customer will modify from your suggest.

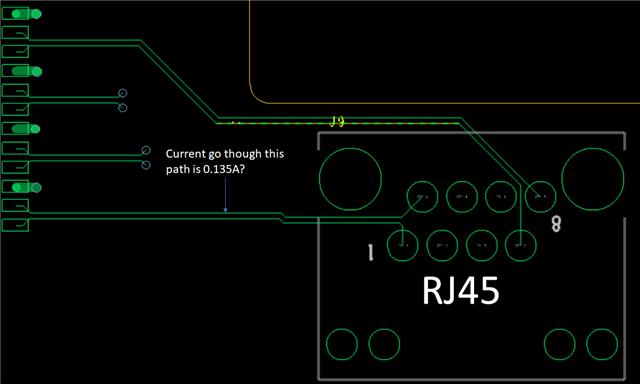

the drain path is too narrow. The entire primary side current is flowing through this trace, it should be bigger.

- How width could support the current?

For Vin= 48V、P=13W、I=P/V=0.27A

1. For 802.3at standard : power go though 2 pair.one pair is 0.135A?

2. The width of every trace just support 0.135A is enough? is 10oz 1mil ok?

Many thanks

Denny

Hey Denny,

Great question.

In the EVM, we use 30mils for this power stage. In higher power, we use wider traces.

To small of traces will drop efficiency and could become a thermal issue.

If this post answers your question, please indicate so by marking this thread as resolved. Thank you.

Regards,

Michael P.

Applications Engineer

Texas Instruments

Hi Michael

Thanks your recommend.

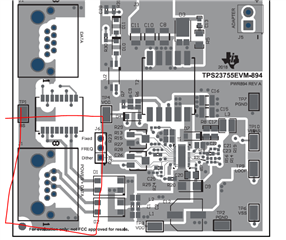

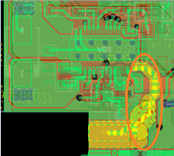

The customer already modified the layout. Could you help to review?

- D29 needs to be as close to the IC as possible. it should also have at least two vias per pad

- the input bulk cap should be closer to the IC as well.

- the drain path is too narrow. The entire primary side current is flowing through this trace, it should be bigger.

- Both RSNS resistors should have more vias

Many thanks

Denny

Hey Denny,

I reviewed these changes and they look good. Thank you!

I assume they did not change anything else.

If this post answers your question, please indicate so by marking this thread as resolved. Thank you.

Regards,

Michael P.

Applications Engineer

Texas Instruments