Dear Teams,

Could you help check following question from my customer?

Problem: As the power input VBUS dropped from 5V to about 2.2V, the output of TPS62290DRVT changed from normal 1.15V to about 2.9V, which caused serious load heating.

Experiment procedure:

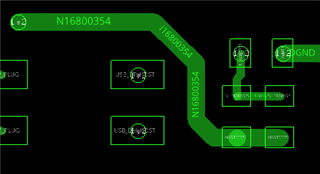

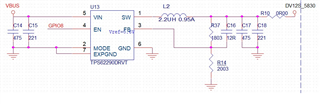

The circuit board uses TPS62290DRVT to supply power to a chip core, the power supply voltage is 1.15V, and the current is about 60mA. The chip itself has an LDO inside, and the measured voltage is about 1V, but the power consumption is relatively high, so an external DC-DC power supply is used to reduce power consumption.

VBUS is powered by the USB port of the computer. There is no problem with this circuit board directly plugged into the USB port. TPS62290DRVT can work normally, but the VBUS of this circuit board needs to be connected to another product, which needs to support hot plugging. The problem occurs in hot plugging. When pulling.

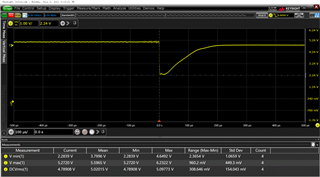

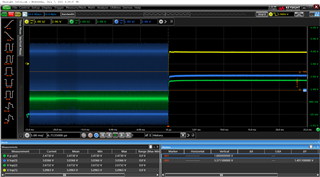

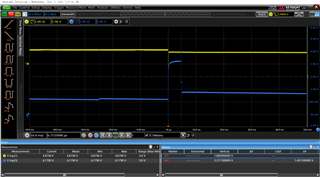

When this circuit board is inserted into another product, because this product has a larger starting current, the VBUS drops from 5V to about 2.2V, as shown in the figure below.

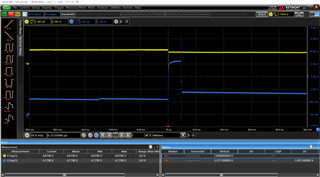

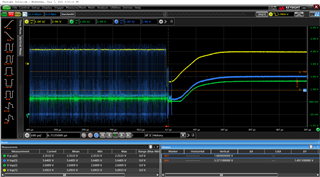

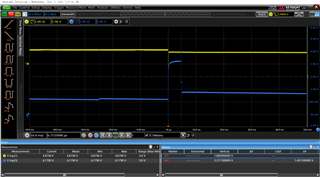

Due to the drop of VBUS, TPS62290DRVT began to work abnormally, and the voltage became about 2.9V, which caused the load current to directly increase to 600mA, and the chip became hot. After re-power on, all can work normally. The signal waveform of abnormal operation was measured with an oscilloscope. As shown in the figure below, the yellow line is VBUS, the green line is the output voltage 1.15V, and the blue line is the SW pin.

The minimum operating voltage given in the specification is 2.3V. We tested it with a switching power supply, and it stopped working at a minimum of 1.85V, but VBUS did not drop to 1.85V. Even if it is lower than 2.3V and does not work, and then VBUS rises again, it stands to reason that TPS62290DRVT should resume normal operation, but the result is like the waveform collected in the figure-the output voltage becomes 2.9V, SW pin There is no PWM wave anymore.

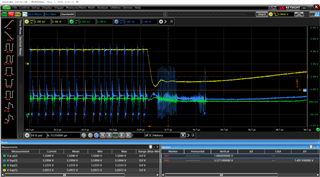

After removing the load, the TPS62290DRVT is in light load mode, and the state of the SW pin is measured, as shown in the figure below. It is found that VBUS can work normally before it drops, and SW has a switching waveform after a period of time; after VBUS drops, the SW pin suddenly rises, then suddenly drops, and then slowly falls back, and no PWM wave is found. After a period of time, there is no PWM wave. It works normally again, there is no abnormal voltage, which is not the same as when there is a load

So based on the results of the above measurement, I don’t understand why this phenomenon occurs. The drop of VBUS is a problem, but when there is a load and no load, what causes these two waveforms? ? ? Both of these phenomena present certain risks to users.

Thanks!

Dylan