Hi Team

My customers has a SCH need you review, please help him

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Jiahui,

Thanks for reaching out.

1. Double check their inductance value with the EVM. I can't see it on their schematic and it is an important parameter.

2. Suggest having a .47 uF cap on the VBUS pin. Please refer to the EVM.

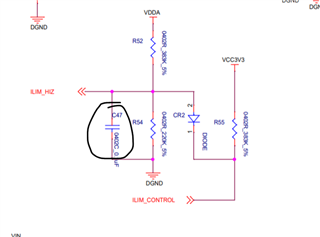

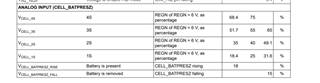

3. I think they can use a smaller capacitance for C47. Such as 100 pF like on the EVM.

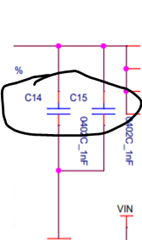

4. Recommend a .01 uF and 1000 pF (1 nF) here (similar to the EVM) instead of two 1 nF caps.

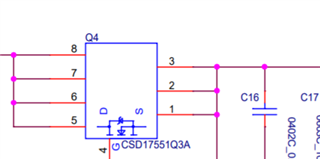

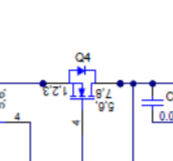

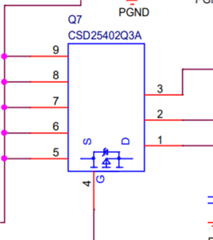

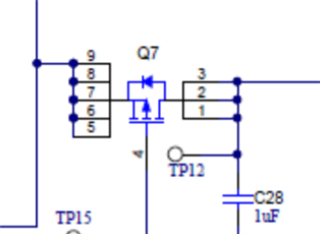

5. Q4 NMOS source and drain orientation is not correct. *customer schematic

*customer schematic *EVM schematic

*EVM schematic

6. This PMOS symbol looks a bit weird..... *customer schematic

*customer schematic *EVM schematic

*EVM schematic

7. Ensure there are pullups somewhere on the schematic for SDA, SCL.

8. On CELL_BATPRES. They can have the voltage divider range closer to the datasheet numbers. They don't need to refer to EVM for this part.

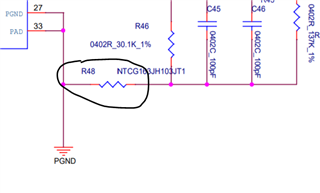

9. I find it weird to have a thermistor here? The EVM has a net-tie, but that is essentially just a copper wire.

So I do see that they referenced the EVM quite a bit(not to say it is bad), but I would tailor the schematic for their own applications and only referenced the necessary parts. For example, CELL_CONTROL mosfet circuit may not be necessary in a production design.

Thanks and I hope this helps,

Peng

*If my answer solves your question, please press "This Resolved My Issue" on the thread.